www.ti.com

Registers

3.4 Interrupt Identification Register (IIR)

The interrupt identification register (IIR) is a read-only register at the same address as the FIFO control

register (FCR), which is a write-only register. When an interrupt is generated and enabled in the interrupt

enable register (IER), IIR indicates that an interrupt is pending in the IPEND bit and encodes the type of

interrupt in the INTID bits. IIR is shown in Figure 12 and described in Figure 12.

The UART has an on-chip interrupt generation and prioritization capability that permits flexible

communication with the CPU. The UART provides three priority levels of interrupts:

• Priority 1 - Receiver line status (highest priority)

• Priority 2 - Receiver data ready or receiver timeout

• Priority 3 - Transmitter holding register empty

The FIFOEN bit in IIR can be checked to determine whether the UART is in the FIFO mode or the

non-FIFO mode.

Access consideration:

IIR and FCR share one address. Regardless of the value of the DLAB bit in LCR, reading from the

address gives the content of IIR, and writing to the address modifies FCR.

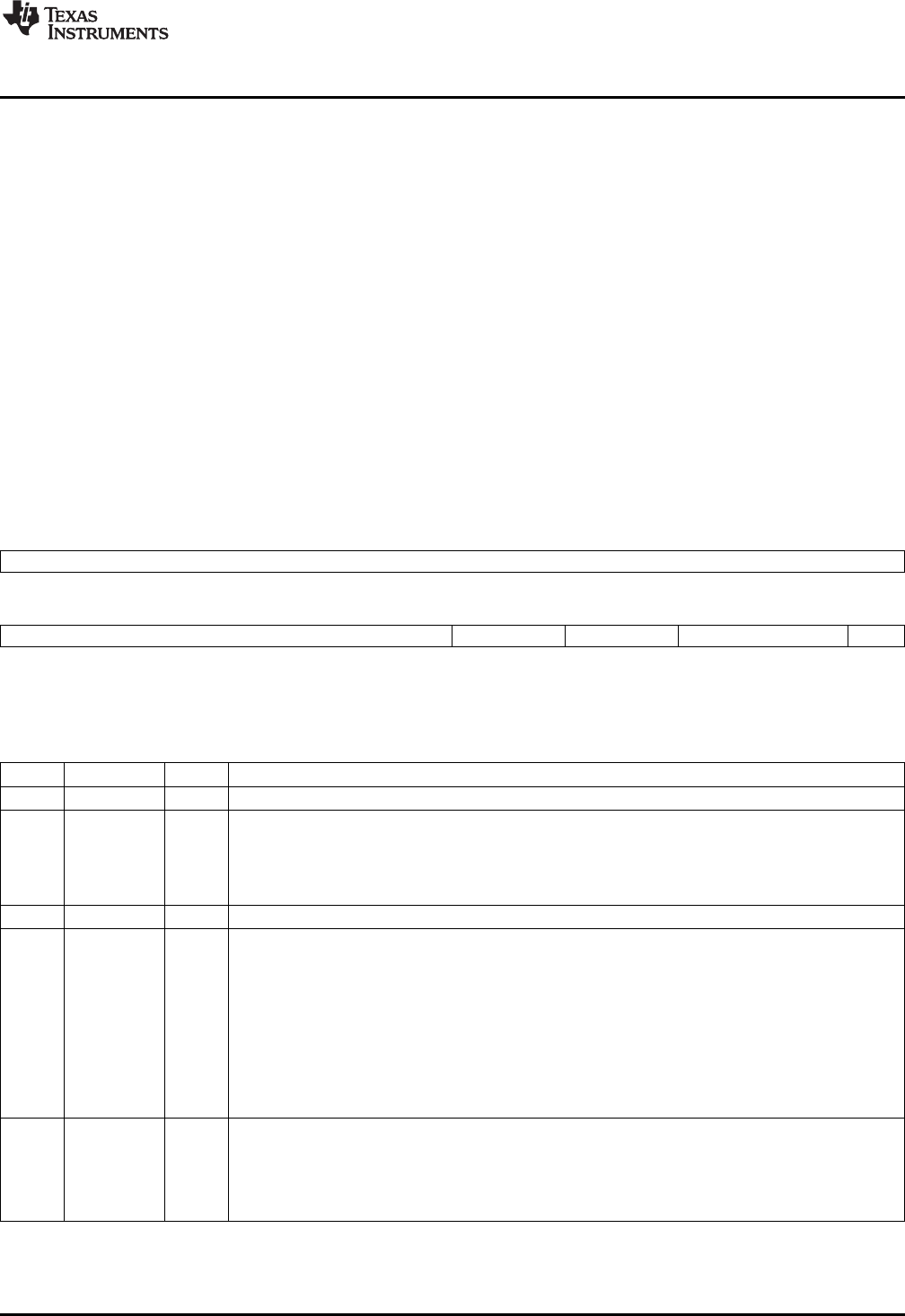

Figure 12. Interrupt Identification Register (IIR)

31 16

Reserved

R-0

15 8 7 6 5 4 3 1 0

Reserved FIFOEN Reserved INTID IPEND

R-0 R-0 R-0 R-0 R-1

LEGEND: R = Read only; -n = value after reset

Table 10. Interrupt Identification Register (IIR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved

7-6 FIFOEN 0-3h FIFOs enabled.

0 Non-FIFO mode

1h-2h Reserved

3h FIFOs are enabled. FIFOEN bit in the FIFO control register (FCR) is set to 1.

5-4 Reserved 0 Reserved

3-1 INTID 0-7h Interrupt type. See Table 11.

0 Reserved

1h Transmitter holding register empty (priority 3)

2h Receiver data available (priority 2)

3h Receiver line status (priority 1, highest)

4h-5h Reserved

6h Character timeout indication (priority 2)

7h Reserved

0 IPEND Interrupt pending. When any UART interrupt is generated and is enabled in IER, IPEND is forced to 0.

IPEND remains 0 until all pending interrupts are cleared or until a hardware reset occurs. If no interrupts

are enabled, IPEND is never forced to 0.

0 Interrupts pending.

1 No interrupts pending.

25

SPRU997C–December 2009 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated