40

3.3.1 Advanced Chipset Control

This section allows you to fine tune the chipset configuration.

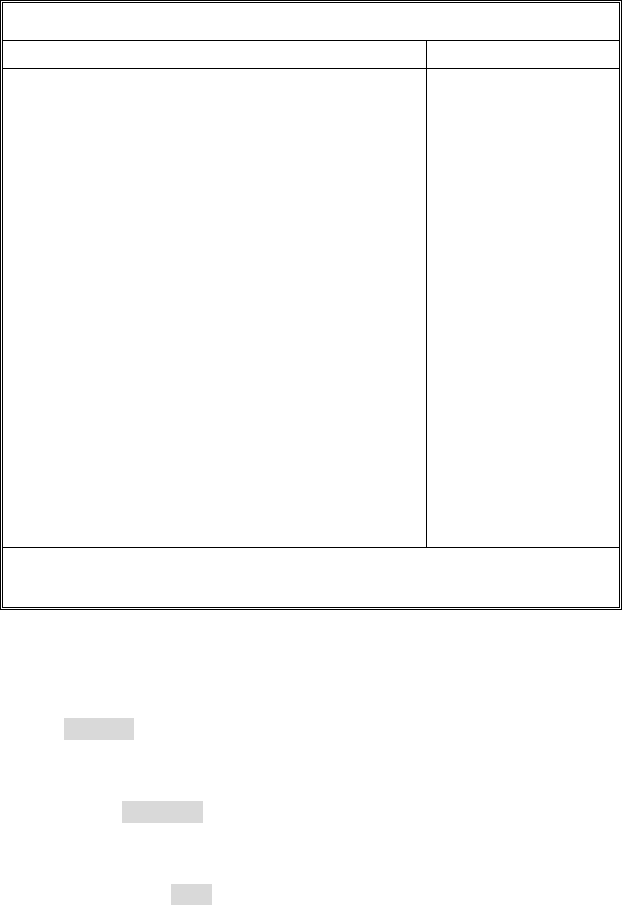

PhoenixBIOS Setup Utility

Main Advanced Security Power Boot Exit

Advanced Chipset Control

Item Specific Help

X ICH USB Control Sub-Menu

X Slot PCI-E (x4 Port) Sub-Menu

X Slot PCI-E (x8 Port) Sub-Menu

X LAN Control Sub-Menu

Crystal Beach Configure Enable

SERR signal condition

PCI-X Frequency

4GB PCI Hole Granularity

Memory Branch Mode

Branch 0 Rank Sparing

Enhanced x8 Detection

Force ITK Config Clocking

WatchDog Mode

WatchDog Timer

Enable Multimedia Timer

Parallel ATA:

Serial ATA:

SATA Controller Mode Option

Native Mode Operation:

[Enable]

[Single bit]

[Auto]

[1.0GB ]

[Interleave]

[Disabled]

[Enabled]

[Disabled]

[Disabled]

[10 Min]

[No]

[Enabled]

[Enabled]

[Compatible]

[Auto]

F1 Help Select Item -/+ Change Values F9 Setup Defaults

Esc Exit Select Menu Enter Select

X Sub-Menu F10 Save and Exit

Crystal Beach Configure Enable

Enable the configuration of memory mapped accesses to the Crystal Beach

Configuration space located in Device 8, Fn 0 and Fn 1. Select Enabled to

support IOAT function.

Enabled / Disabled

SERR signal condition

Select ECC error conditions that SERR# be asserted.

None / Single bit / Multiple bit/ Both

PCI-X Frequency

This option is used to determine the frequency at PCI-X bus.

PCI 66MHz / Auto / PCI-X 66MHz / PCI-X 100MHz / PCI-X 133MHz