3 - Programming the DC Source

34

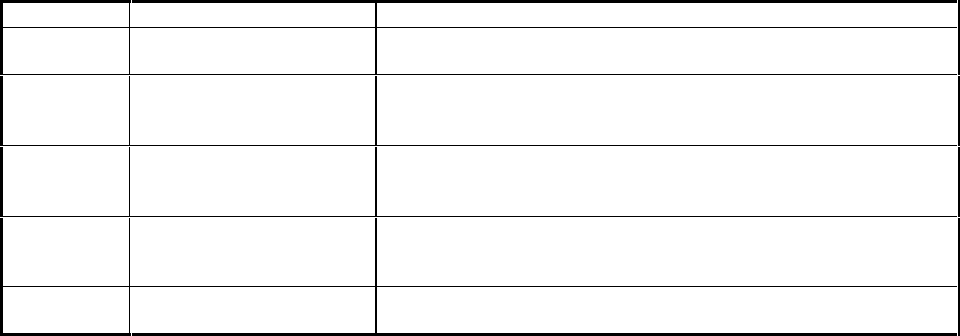

Questionable Status Group

The Questionable Status registers record signals that indicate abnormal operation of the dc source. As

shown in figure 3-7, the group consists of the same type of registers as the Status Operation group. The

outputs of the Questionable Status group are logically-ORed into the QUEStionable summary bit (3) of the

Status Byte register.

Register Command Description

Condition STAT:QUES:COND? A register that holds real-time status of the circuits being

monitored. It is a read-only register.

PTR Filter STAT:QUES:PTR <n> A positive transistion filter that functions as described under

STAT:QUES:NTR|PTR commands in chapter 4. It is a

read/write register.

NTR Filter STAT:QUES:NTR <n> A negative transition filter that functions as described under

STAT:QUES:NTR|PTR commands in chapter 4. It is a

read/write register.

Event STAT:QUES:EVEN? A register that latches any condition that is passed through the

PTR or NTR filters. It is a read-only register that is cleared

when read.

Enable STAT:QUES:ENAB <n> A register that functions as a mask for enabling specific bits

from the Event register. It is a read/write register..

Standard Event Status Group

This group consists of an Event register and an Enable register that are programmed by Common

commands. The Standard Event event register latches events relating to instrument communication status

(see figure 3-7). It is a read-only register that is cleared when read. The Standard Event enable register

functions similarly to the enable registers of the Operation and Questionable status groups.

Command Action

*ESE

programs specific bits in the Standard Event enable register.

*PSC ON

clears the Standard Event enable register at power-on.

*ESR?

reads and clears the Standard Event event register.

The PON (Power On) Bit

The PON bit in the Standard Event event register is set whenever the dc source is turned on. The most

common use for PON is to generate an SRQ at power-on following an unexpected loss of power. To do

this, bit 7 of the Standard Event enable register must be set so that a power-on event registers in the ESB

(Standard Event Summary Bit), bit 5 of the Service Request Enable register must be set to permit an SRQ

to be generated, and *PSC OFF must be sent. The commands to accomplish these conditions are:

*PSC OFF *ESE 128 *SRE 32

Status Byte Register

This register summarizes the information from all other status groups as defined in the

IEEE 488.2

Standard Digital Interface for Programmable Instrumentation

. The bit configuration is shown in Table 3-1.

Command Action

*STB? reads the data in the register but does not clear it (returns MSS in bit 6)

serial poll clears RQS inside the register and returns it in bit position 6 of the response.