Language Dictionary - 4

65

*ESE

This command programs the Standard Event Status Enable register bits. The programming determines

which events of the Standard Event Status Event register (see *ESR?) are allowed to set the ESB (Event

Summary Bit) of the Status Byte register. A "1" in the bit position enables the corresponding event. All of

the enabled events of the Standard Event Status Event Register are logically ORed to cause the Event

Summary Bit (ESB) of the Status Byte Register to be set. The query reads the Standard Event The query

reads the Standard Event Status Enable register.

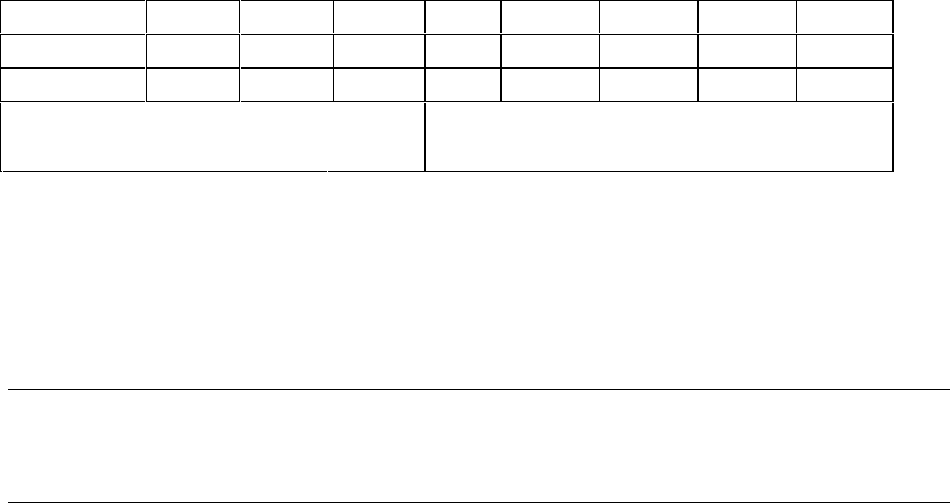

Table 4-6. Bit Configuration of Standard Event Status Enable Register

Bit Position 7 6 5 4 3 2 1 0

Bit Name PON 0 CME EXE DDE QUE 0 OPC

Bit Weight 128 64 32 16 8 4 2 1

PON = Power-on has occurred

CME = Command error

EXE = Execution error

DDE = Device-dependent error

QUE = Query error

OPC = Operation complete

Command Syntax

*ESE <NRf>

Parameters

0 to 255

Power-On Value

(See *PSC)

Examples

*ESE 129

Query Syntax

*ESE?

Returned Parameters

<NR1>(Register value)

Related Commands

*ESR? *PSC *STB?

CAUTION: If *PSC is programmed to 0, the *ESE command causes a write cycle to nonvolatile

memory. Nonvolatile memory has a finite maximum number of write cycles. Programs

that repeatedly cause write cycles to nonvolatile memory can eventually exceed the

maximum number of write cycles and cause the memory to fail.

*ESR?

This query reads the Standard Event Status Event register. Reading the register clears it. The bit

configuration is the same as the Standard Event Status Enable register (see *ESE).

Query Syntax

*ESR?

Parameters

None

Returned Parameters

<NR1>(Register binary value)

Related Commands

*CLS *ESE *ESE? *OPC

*OPC

This command causes the instrument to set the OPC bit (bit 0) of the Standard Event Status register when

the has completed all pending operations. (See *ESE for the bit configuration of the Standard Event

Status register.)

Pending operations

are complete when:

u all commands sent before *OPC have been executed. This includes overlapped commands. Most

commands are sequential and are completed before the next command is executed. Overlapped

commands are executed in parallel with other commands. Commands that affect output voltage,

current or state, relays, and trigger actions are overlapped with subsequent commands sent to the

dc source. The *OPC command provides notification that all overlapped commands have been

completed.

u all triggered actions are completed