CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 24 of 83

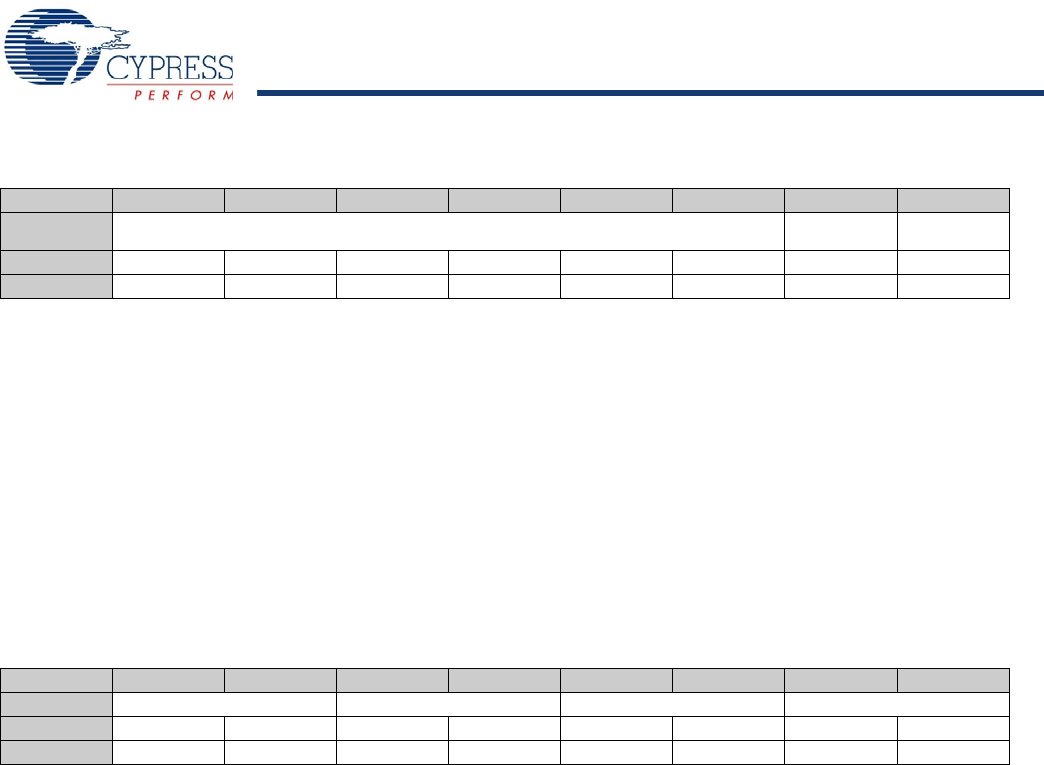

Table 10-5. USB Osclock Clock Configuration (OSCLCKCR) [0x39] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field Reserved Fine Tune Only USB Osclock

Disable

Read/Write – – – – – – R/W R/W

Default 0 0 0 0 0 0 0 0

This register is used to trim the Internal 24 MHz Oscillator using received low speed USB packets as a timing reference. The

USB Osclock circuit is active when the Internal 24 MHz Oscillator provides the USB clock.

Bit [7:2]: Reserved

Bit 1: Fine Tune Only

0 = Fine and Course tuning

1 = Disable the oscillator lock from performing the coarse-tune portion of its retuning. The oscillator lock must be allowed to

perform a coarse tuning to tune the oscillator for correct USB SIE operation. After the oscillator is properly tuned, this bit is set

to reduce variance in the internal oscillator frequency that would be caused course tuning.

Bit 0: USB Osclock Disable

0 = Enable. With the presence of USB traffic, the Internal 24 MHz Oscillator precisely tunes to 24 MHz ± 1.5%

1 = Disable. The Internal 24 MHz Oscillator is not trimmed based on USB packets. This setting is useful when the internal

oscillator is not sourcing the USBSIE clock.

Table 10-6. Timer Clock Config (TMRCLKCR) [0x31] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field TCAPCLK Divider TCAPCLK Select ITMRCLK Divider ITMRCLK Select

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 1 0 0 0 1 1 1 1

Bit [7:6]: TCAPCLK Divider [1:0]

TCAPCLK Divider controls the TCAPCLK divisor.

0 0 = Divider Value 2

0 1 = Divider Value 4

1 0 = Divider Value 6

1 1 = Divider Value 8

Bit [5:4]: TCAPCLK Select

The TCAPCLK Select field controls the source of the TCAPCLK.

0 0 = Internal 24 MHz Oscillator

0 1 = External clock—external clock at CLKIN (P0.0) input.

1 0 = Internal 32 kHz low power oscillator

1 1 = TCAPCLK Disabled

Note The 1024 μs interval timer is based on the assumption that TCAPCLK is running at 4 MHz. Changes in TCAPCLK frequency

causes a corresponding change in the 1024 μs interval timer frequency.

Bit [3:2]: ITMRCLK Divider

ITMRCLK Divider controls the ITMRCLK divisor.

0 0 = Divider value of 1

0 1 = Divider value of 2

1 0 = Divider value of 3

1 1 = Divider value of 4

Bit [1:0]: ITMRCLK Select

0 0 = Internal 24 MHz Oscillator

0 1 = External clock—external clock at CLKIN (P0.0) input.

1 0 = Internal 32 kHz low power oscillator

1 1 = TCAPCLK

[+] Feedback [+] Feedback