CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 33 of 83

14. General Purpose IO (GPIO) Ports

14.1 Port Data Registers

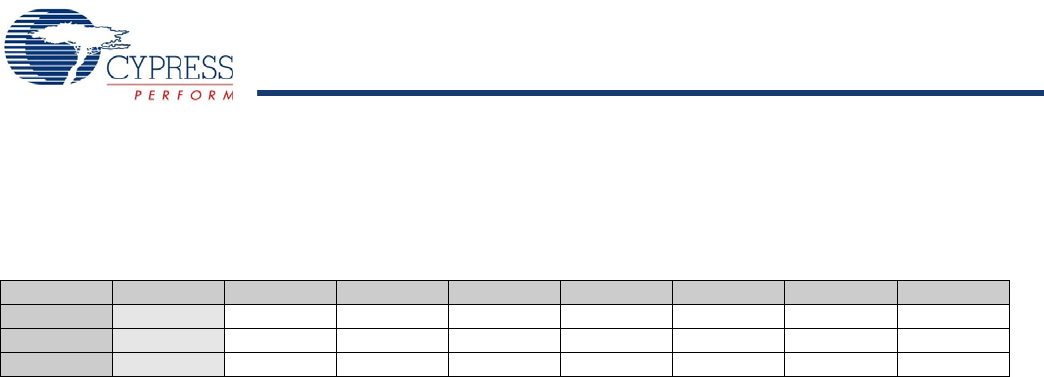

Table 14-1. P0 Data Register (P0DATA)[0x00] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field P0.7 P0.6/TIO1 P0.5/TIO0 P0.4/INT2 P0.3/INT1 P0.2/INT0 P0.1/CLKOUT P0.0/CLKIN

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 000 0

This register contains the data for Port 0. Writing to this register sets the bit values to be output on output enabled pins. Reading

from this register returns the current state of the Port 0 pins.

Bit 7: P0.7 Data

P0.7 only exists in the CY7C638xx

Bit [6:5]: P0.6–P0.5 Data/TIO1 and TIO0

Besides their use as the P0.6–P0.5 GPIOs, these pins are also used for the alternate functions as the Capture Timer input or

Timer output pins (TIO1 and TIO0). To configure the P0.5 and P0.6 pins, refer to the P0.5/TIO0–P0.6/TIO1 Configuration Register

(Table 14-8 on page 37).

The use of the pins as the P0.6–P0.5 GPIOs and the alternate functions exist in all the enCoRe II parts.

Bit [4:2]: P0.4–P0.2 Data/INT2 – INT0

Besides their use as the P0.4–P0.2 GPIOs, these pins are also used for the alternate functions as the Interrupt pins (INT0–INT2).

To configure the P0.4–P0.2 pins, refer to the P0.2/INT0–P0.4/INT2 Configuration Register (Table 14-7 on page 37).

The use of the pins as the P0.4–P0.2 GPIOs and the alternate functions exist in all the enCoRe II parts.

Bit 1: P0.1/CLKOUT

Besides its use as the P0.1 GPIO, this pin is also used for an alternate function as the CLK OUT pin. To configure the P0.1 pin,

refer to the P0.1/CLKOUT Configuration Register (Table 14-6 on page 36).

Bit 0: P0.0/CLKIN

Besides its use as the P0.0 GPIO, this pin is also used for an alternate function as the CLKIN pin. To configure the P0.0 pin,

refer to the P0.0/CLKIN Configuration Register (Table 14-5 on page 36).

[+] Feedback [+] Feedback