CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 80 of 83

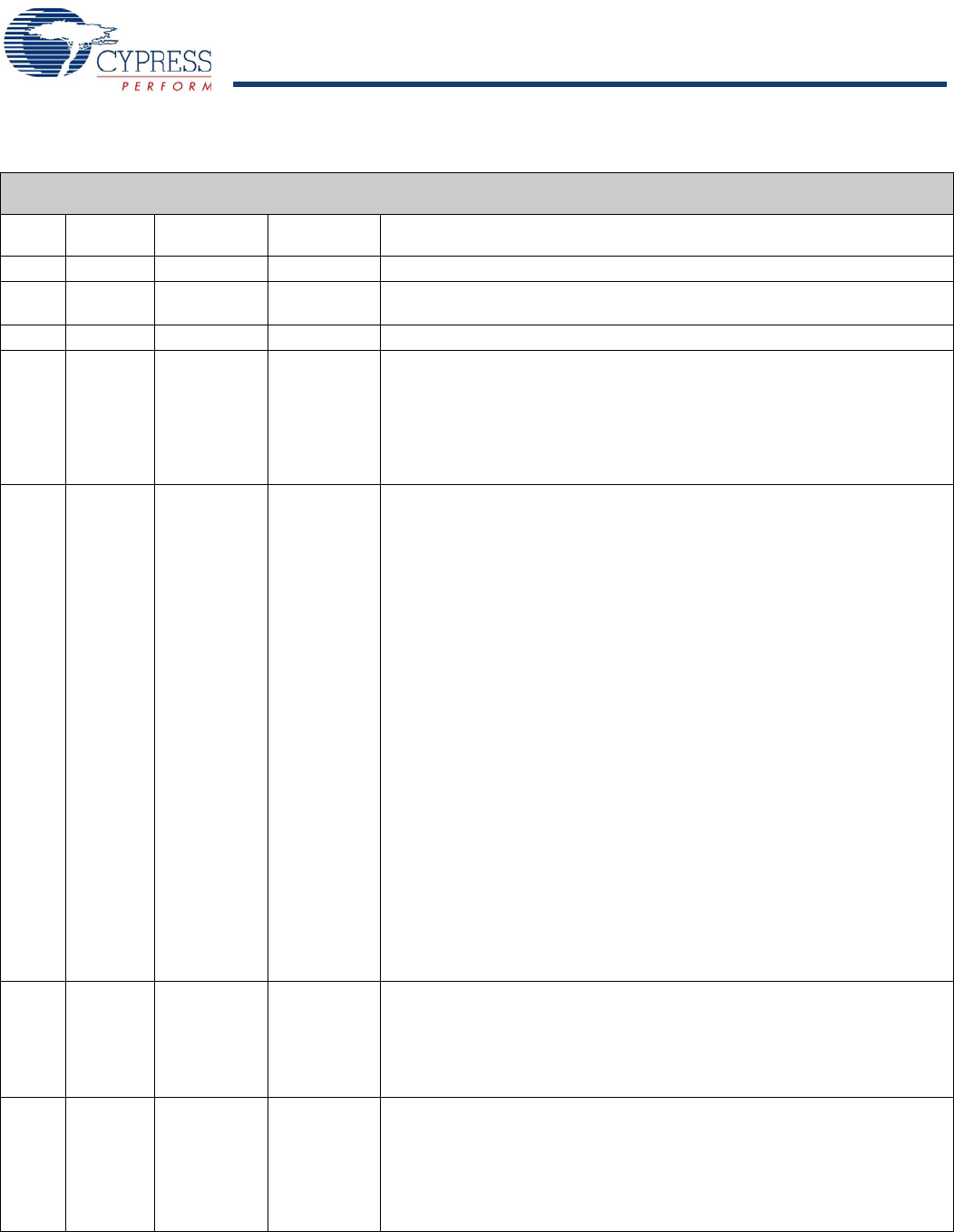

32. Document History Page

Document Title: CY7C63310, CY7C638xx enCoRe™ II Low Speed USB Peripheral Controller

Document Number: 38-08035

Rev. ECN No.

Orig. of

Change

Submission

Date

Description of Change

** 131323 XGR 12/11/03 New data sheet

*A 221881 KKU See ECN Added Register descriptions and package information, changed from advance

information to preliminary

*B 271232 BON See ECN Reformatted. Updated with the latest information

*C 299179 BON See ECN Corrected 24-PDIP pinout typo in Table 5-2 on page 6 Added Table 10-1 on

page 21. Updated Table 9-5 on page 16, Table 10-3 on page 22, Table 13-1 on

page 31, Table 17-2 on page 52, Table 17-4 on page 52, Table 17-6 on page

53. and Table 15-2 on page 41. Added various updates to the GPIO Section

(General Purpose IO (GPIO) Ports on page 33) Corrected Table 15-4 on page

42. Corrected Figure 28-7. on page 73 and Figure 28-8. on page 73. Added the

16-pin PDIP package diagram (section Package Diagrams on page 76)

*D 322053 TVR

BON

See ECN Introduction on page 3: Removed Low-voltage reset in last paragraph. There

is no LVR, only LVD (Low voltage detect). Explained more about LVD and POR.

Changed capture pins from P0.0,P0.1 to P0.5,P0.6.

Table 6-1 on page 7: Changed table heading (Removed Mnemonics and made

as Register names).

Table 9-5 on page 16: Included #of rows for different flash sizes.

Clock Architecture Description on page 21: Changed CPUCLK selectable

options from n=0-5,7,8 to n=0-5,7.

Clocking on page 19: Changed ITMRCLK division to 1,2,3,4. Updated the

sources to ITMRCLK, TCAPCLKs. Mentioned P17 is TTL enabled permanently.

Corrected FRT, PIT data write order. Updated INTCLR, INTMSK registers in

the register table also.

DC Characteristics on page 68: changed LVR to LVD included max min

programmable trip points based on char data. Updated the 50ma sink pins on

638xx, 63903. Keep-alive voltage mentioned corresponding to Keep-alive

current of 20uA. Included Notes regarding VOL,VOH on P1.0,P1.1 and TMDO

spec.

AC Characteristics on page 69: T

MDO1

, T

SDO1

In description column changed

Phase to 0.

Pinouts on page 4: Removed the VREG from the CY7C63310 and CY7C63801

Removed SCLK and SDATA. Created a separate pinout diagram for the

CY7C63813.

Added the GPIO Block Diagram (Figure 14-1. on page 36)

Table 10-4 on page 23: Changed the Sleep Timer Clock unit from 32 kHz count

to Hz.

Table 21-1 on page 58: Added more descriptions to the register.

*E 341277 BHA See ECN Corrected V

IH

TTL value in DC Characteristics on page 68.

Updated V

IL

TTL value.

Added footnote to pin description table for D+/D– pins.

Added Typical Values to Low Voltage Detect table.

Corrected Pin label on 16-pin PDIP package.

Corrected minor typos.

*F 408017 TYJ See ECN Table 5-2 on page 6: Corrected pin assignment for the 24-pin QSOP package

- GPIO port 3

New Assignments: Pin 19 assigned to P3.0 and pin 20 to P3.1

Table 17-7 on page 54: INT_MASK1 changed to 0xE1

Table 17-8 on page 55: INT_MASK0 changed to 0xE0

Register Summary on page 64: Register Summary, address E0 assigned to

INT_MASK0 and address E1 assigned to INT_MASK1

[+] Feedback [+] Feedback