CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 58 of 83

21. USB Device

21.1 USB Device Address

21.2 Endpoint 0, 1, and 2 Count

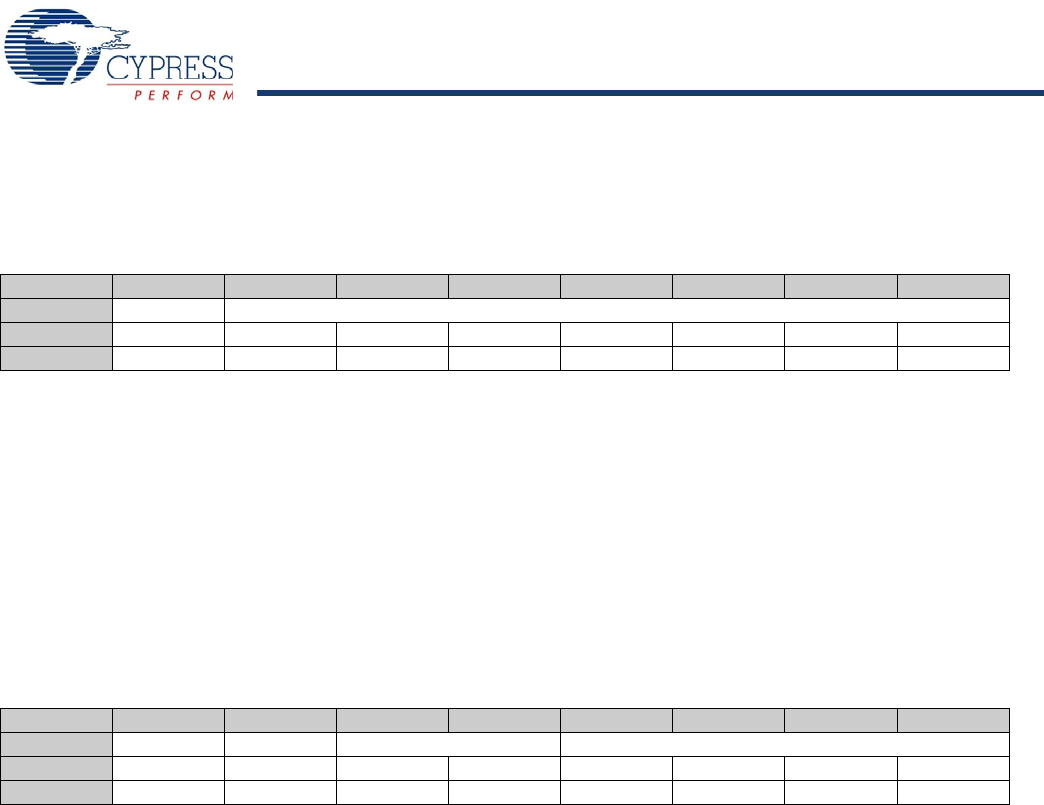

Table 21-1. USB Device Address (USBCR) [0x40] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field USB Enable Device Address[6:0]

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 000 0

Bit 7: USB Enable

This bit must be enabled by firmware before the serial interface engine (SIE) responds to the USB traffic at the address specified

in Device Address [6:0]. When this bit is cleared, the USB transceiver enters power down state. User’s firmware must clear this

bit before entering sleep mode to save power.

0 = Disable USB device address and put the USB transceiver into power down state.

1 = Enable USB device address and put the USB transceiver into normal operating mode.

Bit [6:0]: Device Address [6:0]

These bits must be set by firmware during the USB enumeration process (that is, SetAddress) to the nonzero address assigned

by the USB host.

Table 21-2. Endpoint 0, 1, and 2 Count (EP0CNT–EP2CNT) [0x41, 0x43, 0x45] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field Data Toggle Data Valid Reserved Byte Count[3:0]

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 000 0

Bit 7: Data Toggle

This bit selects the DATA packet's toggle state. For IN transactions, firmware must set this bit to select the transmitted Data

Toggle. For OUT or SETUP transactions, the hardware sets this bit to the state of the received Data Toggle bit.

0 = DATA0

1 = DATA1

Bit 6: Data Valid

This bit is used for OUT and SETUP tokens only. This bit is cleared to ‘0’ if CRC, bitstuff, or PID errors have occurred. This bit

does not update for some endpoint mode settings.

0 = Data is invalid. If enabled, the endpoint interrupt occurs even if invalid data is received.

1 = Data is valid

Bit [5:4]: Reserved

Bit [3:0]: Byte Count Bit [3:0]

Byte Count Bits indicate the number of data bytes in a transaction: For IN transactions, firmware loads the count with the number

of bytes to be transmitted to the host from the endpoint FIFO. Valid values are 0 to 8 inclusive. For OUT or SETUP transactions,

the count is updated by hardware to the number of data bytes received, plus 2 for the CRC bytes. Valid values are 2–10 inclusive.

For Endpoint 0 Count Register, when the count updates from a SETUP or OUT transaction, the count register locks and cannot

be written by the CPU. Reading the register unlocks it. This prevents firmware from overwriting a status update on it.

[+] Feedback [+] Feedback