CY7C63310, CY7C638xx

Document 38-08035 Rev. *K Page 70 of 83

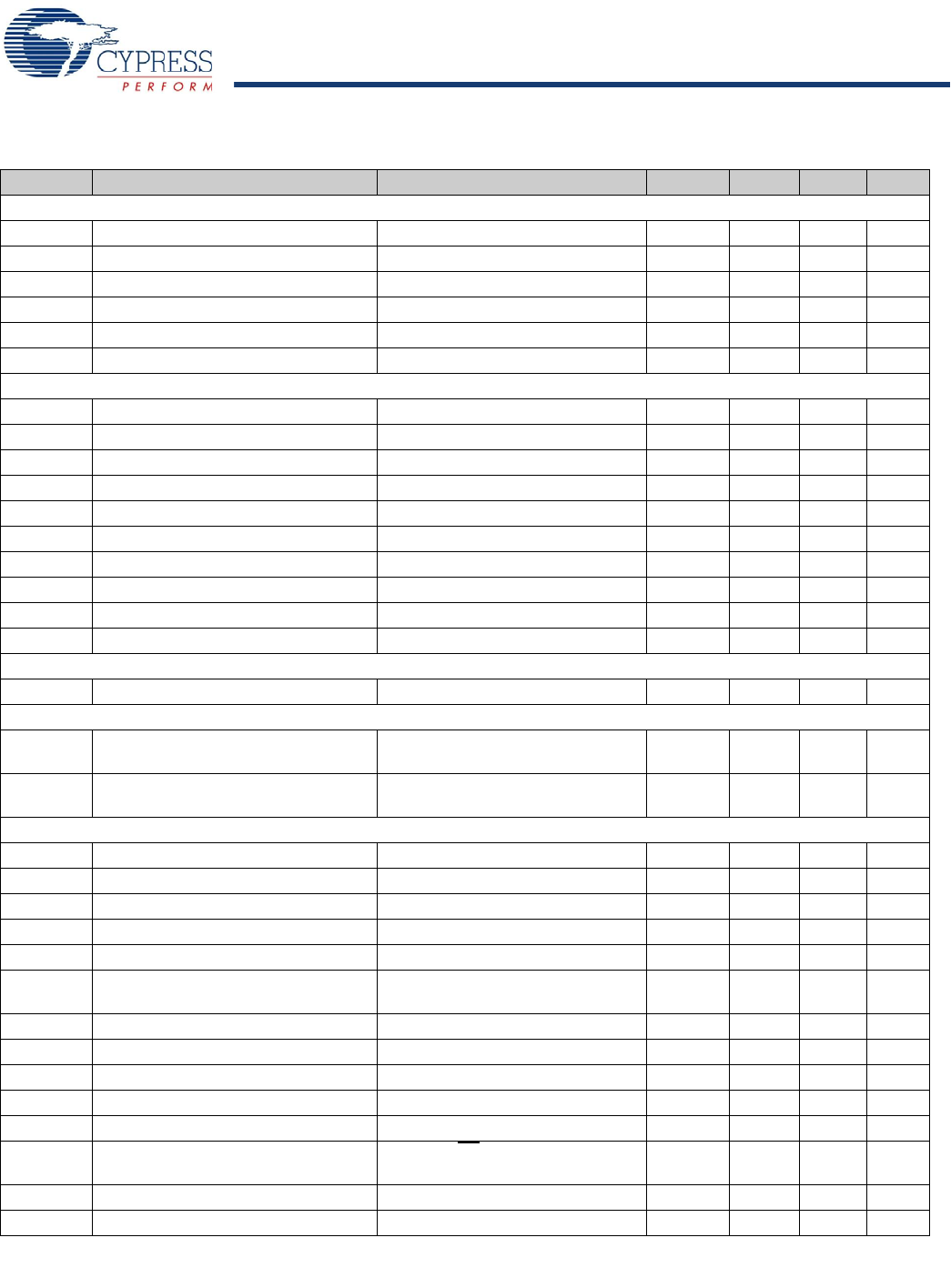

USB Driver

T

R1

Transition Rise Time C

LOAD

= 200 pF 75 ns

T

R2

Transition Rise Time C

LOAD

= 600 pF 300 ns

T

F1

Transition Fall Time C

LOAD

= 200 pF 75 ns

T

F2

Transition Fall Time C

LOAD

= 600 pF 300 ns

T

R

Rise/Fall Time Matching 80 125 %

V

CRS

Output Signal Crossover Voltage 1.3 2.0 V

USB Data Timing

T

DRATE

Low Speed Data Rate Average Bit Rate (1.5 Mbps ± 1.5%) 1.4775 1.5225 Mbps

T

DJR1

Receiver Data Jitter Tolerance To next transition –75 75 ns

T

DJR2

Receiver Data Jitter Tolerance To pair transition –45 45 ns

T

DEOP

Differential to EOP Transition Skew –40 100 ns

T

EOPR1

EOP Width at Receiver Rejects as EOP 330 ns

T

EOPR2

EOP Width at Receiver Accept as EOP 675 ns

T

EOPT

Source EOP Width 1.25 1.5 μs

T

UDJ1

Differential Driver Jitter To next transition –95 95 ns

T

UDJ2

Differential Driver Jitter To pair transition –95 95 ns

T

LST

Width of SE0 during Diff. Transition 210 ns

Non-USB Mode Driver Characteristics

T

FPS2

SDATA/SCK Transition Fall Time 50 300 ns

GPIO Timing

T

R_GPIO

Output Rise Time

[8]

Measured between 10 and 90%

Vdd/Vreg with 50 pF load

50 ns

T

F_GPIO

Output Fall Time

[8]

Measured between 10 and 90%

Vdd/Vreg with 50 pF load

15 ns

SPI Timing

T

SMCK

SPI Master Clock Rate F

CPUCLK

/6 2 MHz

T

SSCK

SPI Slave Clock Rate 2.2 MHz

T

SCKH

SPI Clock High Time High for CPOL = 0, Low for CPOL = 1 125 ns

T

SCKL

SPI Clock Low Time Low for CPOL = 0, High for CPOL = 1 125 ns

T

MDO

Master Data Output Time

[10]

SCK to data valid –25 50 ns

T

MDO1

Master Data Output Time,

First bit with CPHA = 0

Time before leading SCK edge 100 ns

T

MSU

Master Input Data Setup time 50 ns

T

MHD

Master Input Data Hold time 50 ns

T

SSU

Slave Input Data Setup Time 50 ns

T

SHD

Slave Input Data Hold Time 50 ns

T

SDO

Slave Data Output Time SCK to data valid 100 ns

T

SDO1

Slave Data Output Time,

First bit with CPHA = 0

Time after SS LOW to data valid 100 ns

T

SSS

Slave Select Setup Time Before first SCK edge 150 ns

T

SSH

Slave Select Hold Time After last SCK edge 150 ns

28. AC Characteristics

(continued)

Parameter Description Conditions Min Typical Max Unit

Note

10. In Master mode, first bit is available 0.5 SPICLK cycle before Master clock edge available on the SCLK pin.

[+] Feedback [+] Feedback