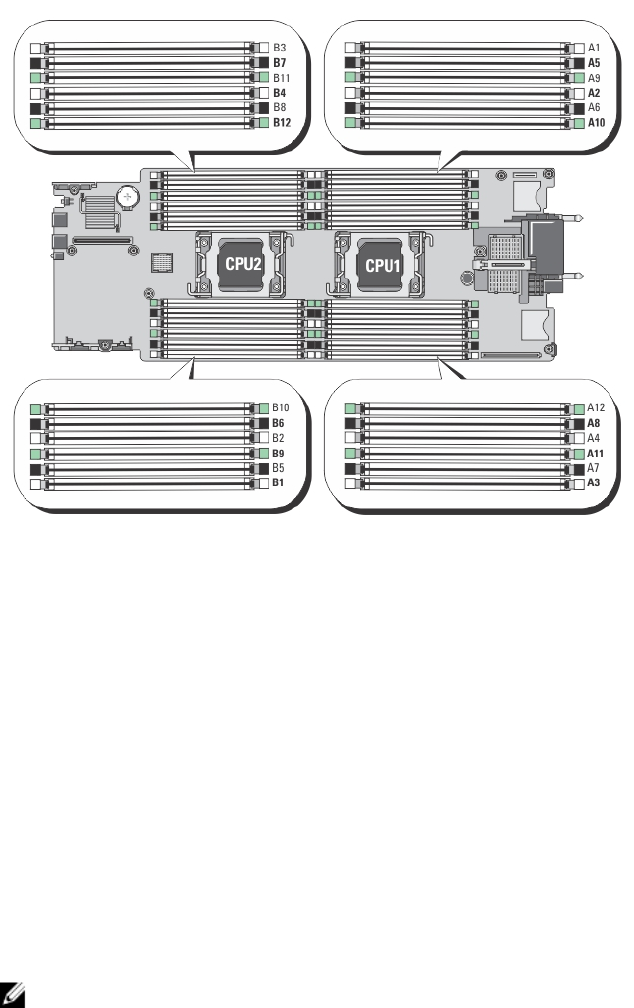

Figure 7. Memory Socket Locations

Memory channels are organized as follows:

Processor 1 channel 0: memory sockets A2, A6, and A10

channel 1: memory sockets A1, A5, and A9

channel 2: memory sockets A4, A8, and A12

channel 3: memory sockets A3, A7, and A11

Processor 2 channel 0: memory sockets B2, B6, and B10

channel 1: memory sockets B1, B5, and B9

channel 2: memory sockets B4, B8, and B12

channel 3: memory sockets B3, B7, and B11

General Memory Module Installation Guidelines

NOTE: Memory configurations that fail to observe these guidelines can prevent your system from starting and

producing any video output, hanging during memory configuration, or operating with reduced memory.

This system supports Flexible Memory Configuration, enabling the system to be configured and run in any valid chipset

architectural configuration. The following are the recommended guidelines for best performance:

• UDIMMs, RDIMMs, and LRDIMMs must not be mixed.

• x4 and x8 DRAM based DIMMs can be mixed. For more information, see Mode-Specific Guidelines.

• A maximum of two UDIMMs can be populated in a channel.

• Up to three LRDIMMs can be populated regardless of rank count.

30