30 RS/6000 43P 7043 Models 150 and 260 Handbook

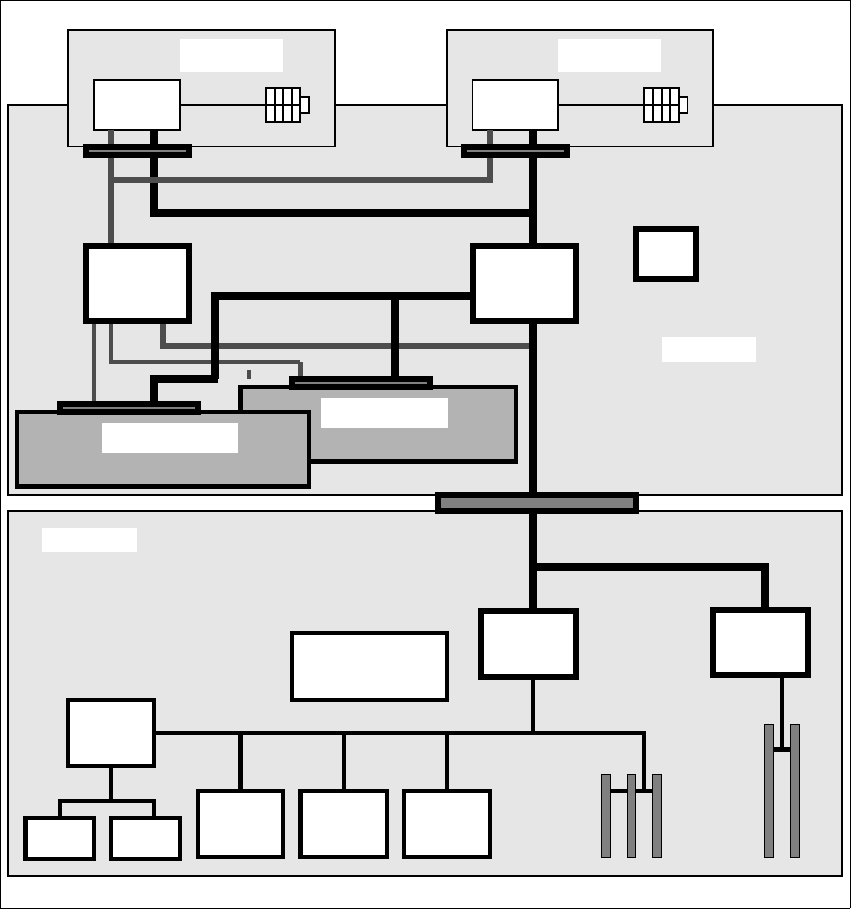

Figure 9. RS/6000 High Level System Block Diagram (Model 260)

The memory controller chip can act as the system interrupt controller, or can

pass interrupts through to an external device. Two distinct interrupt protocols

POWER3

200 MHz

4 MB L2

32 bytes

@ 200 MHz

256 MB - 2 GB

PCI Bridge

PCI Bridge

6XX Data Bus

16 Bytes

100 MHz

6XX Address

100 MHz

3 cycle tenure

Memory Data Bus

16 bytes @ 100 MHz

6XX-MX Bus

66 MHz

3 PCI Slots

32-Bit / 33 MHz

2 PCI Slots

64-Bit / 50 MHz

Memory

Address

ISA Bridge

W83C553

Super I/OAudio

Integrated

POWER3

CPU Card

planar A

planar B

Memory Card

AB4

Clock

Service Processor

256 MB - 2 GB

Memory Card

POWER3

200 MHz

4 MB L2

32 bytes

@ 200 MHz

POWER3

CPU Card

Data

U-SCSIU-SCSI10/100 ETH

Addr/Cntl