44 RS/6000 43P 7043 Models 150 and 260 Handbook

into a previously unreferenced line, the complete line must be fetched from

memory first before the new value can be stored into it. If a cache line is

overwritten by newly accessed data, then, if the data from the old line is

needed again, it must be reloaded and another cache miss taken.

2.5.1.4 Cache Line Prefetch

Because of the relatively large number of cycles needed for a cache miss,

POWER3 has a mechanism for mitigating the performance impact for

sequentially accessed data. For up to four streams of data, the hardware

attempts to detect sequential access and initiates the loading of subsequent

lines in parallel, so they stream into cache behind the first line without waiting

for the miss to occur. This important feature of POWER3 is not present on

POWER2.

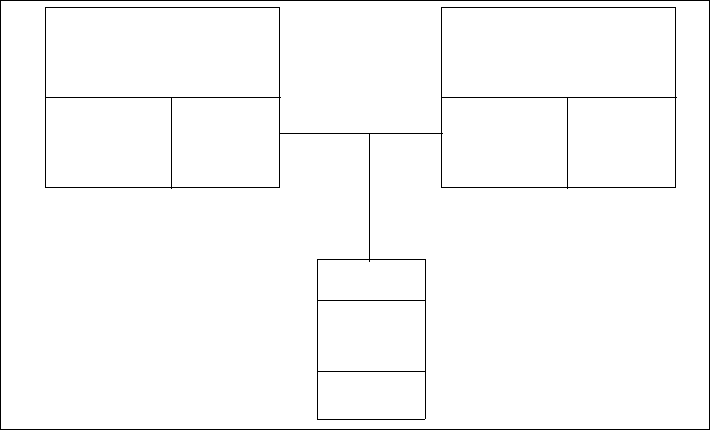

2.5.1.5 Cache Coherency Problem

In an SMP, all of the processors have their own cache to improve data

locality. Only the main memory is shared. Since caches are not shared, it is

necessary to keep all the processors’ caches coherent. The coordination of

current versus stale data between processors is called cache coherency and is

one of the most important issues when designing an SMP system.

Consider an application that runs on two processors, processor 1 and

processor 2, as shown in Figure 16.

Figure 16. SMP Cache Coherency Problem

processor 1

cache A

processor 2

cache B

A

0123:

memory