34 RS/6000 43P 7043 Models 150 and 260 Handbook

2.3.3 The 60X and 6XX Bus

The 60X bus was designed to provide a common interface that supplies

communication between processors, memory controllers, and high-speed I/O

devices. Arbitration on the bus is performed by a central, off-chip arbitrator.

The 60X bus provides the capability to build an SMP system with the MESI

protocol. This bus is also known as the MP System Bus.

The 60X bus uses separate address and data buses and a variety of control

and status signals. The address bus is 32 bits wide (with 4 bits parity) and the

data bus is 64 bits wide (with 8 bits parity). These separate address and data

buses run independently, allowing split transactions. The bus is synchronous,

with all timing relative to the rising edge of the bus clock. Inputs are sampled,

and outputs are driven from this edge.

It is through this bus that the two-way SMP’s processors are attached,

memory is accessed, and cache snooping is achieved.

2.3.4 The 6XX-MX I/O Bus

The 6XX-MX I/O bus is a high-performance bus designed to be used as a

high-end I/O bus for mid- and high-range systems. It will accommodate both

32- and 64-bit processors with real memory addressing extending beyond 32

bits.

The requests and replies are tagged, allowing for out-of-order replies, which

are common for programmed I/O to another bus or in a non-uniform memory

access (NUMA) environment.

This bus must have a bridge chip to translate a 6XX or 60X transaction with

the corresponding operation. Due to the 66 MHz PCI capability as defined in

the PCI Local Bus Specification (Revision 2.1), local bus performance has

increased from 264 MB/s to 528 MB/s for 64-bit transfers.

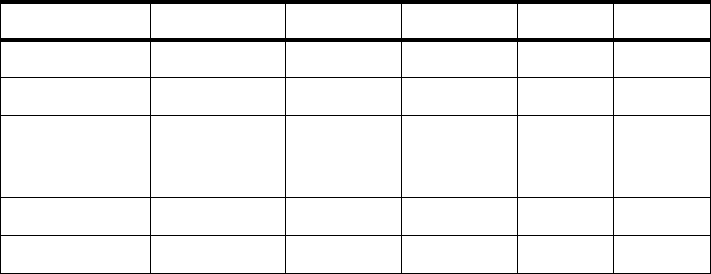

Data Bus 64 64 8 16 16/32

Address Bus 32 64 20 24 24/43

Bus Clock 66 MHz

83 MHz

100 MHz

33 MHz

(32-bit)

4.7 MHz 8.3 MHz 8.3 MHz

Interrupts 4 6 11 11

DMA Channel busmaster 3 7 7

Specification PowerPC PCI ISA(8) ISA(16) EISA