72 RS/6000 43P 7043 Models 150 and 260 Handbook

3.2.2.3 Memory Subsystem

The base configuration comes with 256 MB Error Checking and Correcting

(ECC) SDRAM (2 x 128 MB DIMMs).

The Model 260 has an enhanced memory controller running at 100 MHz

memory bus speed. See 3.1.3.1, “Memory” on page 58 for more information

how the memory can be expanded.

Synchronous DRAM

The SDRAM operates faster than conventional DRAM. The SDRAM can

supply data every 10 nanosecond clock cycle once its initial access time of 60

nanoseconds has been satisfied. As with conventional memory, the SDRAM

banks have a period of latency after an access. During this period, the

memory bank would be designated as busy. To achieve better performance,

another memory bank (already precharged) needs to be accessed during that

period of latency. The memory I/O controller uses heavy queueing to be able

to make an intelligent decision on which memory bank to access next. The

controller will queue up to eight read commands and eight write commands

and attempts to schedule all reads to non-busy banks. It fills in with writes

when no reads are pending.

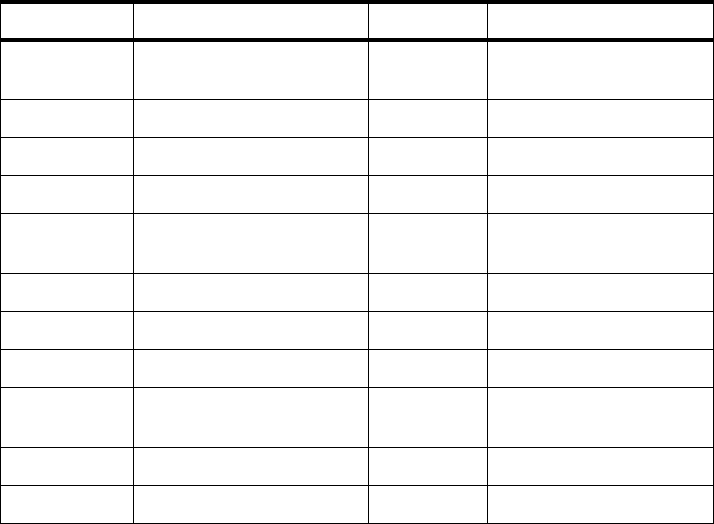

J3 PCI fan connector J4 I/O board connector to

system board

J5 VPD module connector J6 ESP external connector

J7 Internal SCSI connector J8, J9 64-bit PCI connectors

J10 CD ROM Audio J11 Battery connector

J12, J13, J14 32-bit PCI connectors J15 Service processor

external connector

J16 Power connector J17 Diskette drive connector

J18 Tablet connector J19 Power connector

J20 AUI Ethernet connector J21 Cec fan connector

J23 Serial port connector J24 Keyboard/Mouse

connector

J25 RJ45 Ethernet connector J26 Audio in/out

J27 Parallel port connector J28 External SCSI connector

Location Description Location Description