Quad-Core Intel® Xeon® Processor 5400 Series TMDG 21

Thermal/Mechanical Reference Design

smaller foot print and decreased sensitivity to noise. These DTS benefits will result in

more accurate fan speed control and TCC activation.The DTS application in fan speed

control will be discussed in more detail in Section 2.4.1.

2.2.3 Platform Environmental Control Interface (PECI)

The PECI interface is designed specifically to convey system management information

from the processor (initially, only thermal data from the Digital Thermal Sensor). It is a

proprietary single wire bus between the processor and the chipset or other health

monitoring device. The PECI specification provides a specific command set to discover,

enumerate devices, and read the temperature. For an overview of the PECI interface,

please refer to PECI Feature Set Overview. For more detailed information on PECI,

please refer to Platform Environment Control Interface (PECI) Specification and Quad-

Core Intel® Xeon® Processor 5400 Series Datasheet.

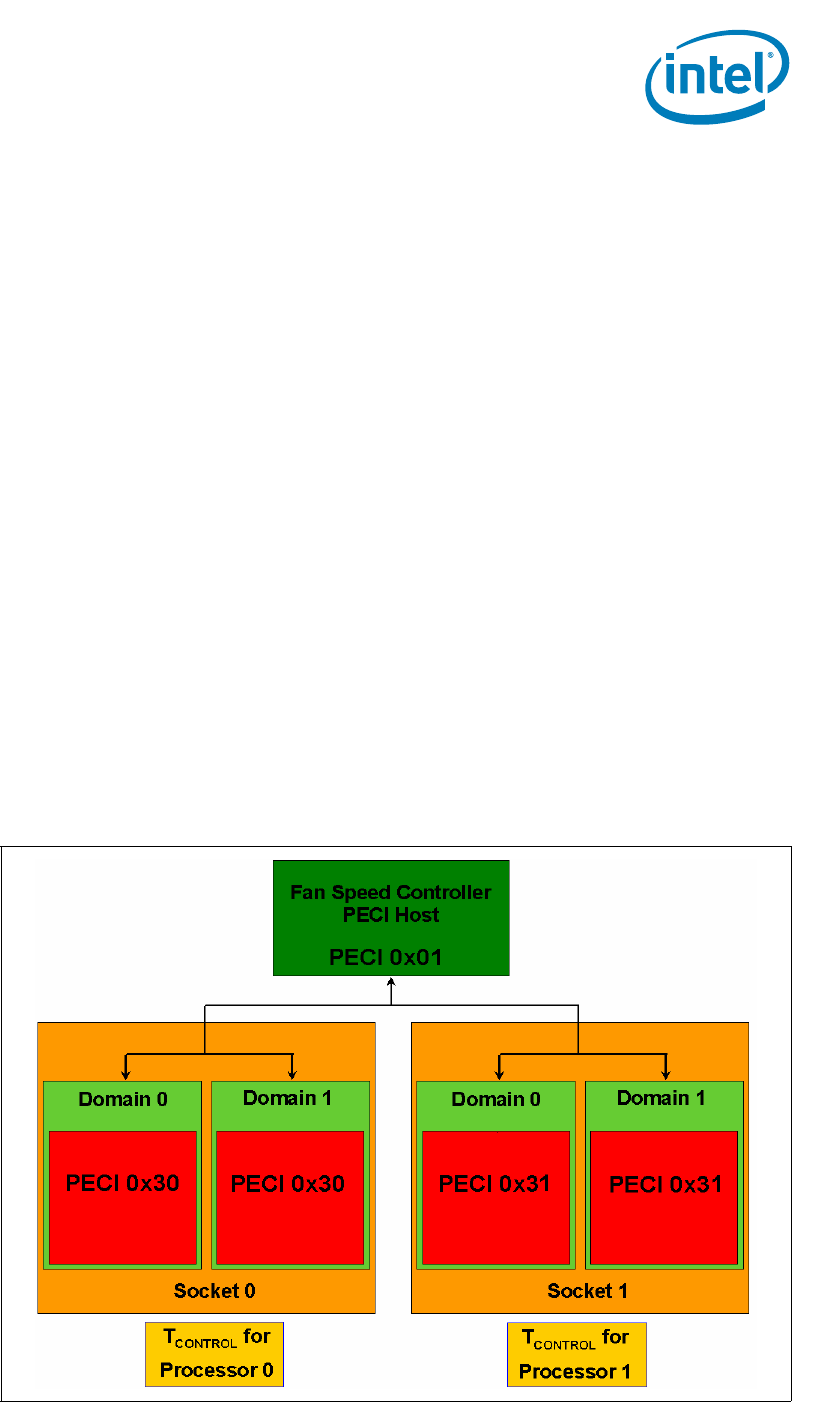

2.2.4 Multiple Core Special Considerations

2.2.4.1 Multiple Digital Thermal Sensor Operation

Each Quad-Core Intel® Xeon® Processor 5400 Series can have multiple Digital

Thermal Sensors located on the die. Each die within the processor currently maps to a

PECI domain. The Quad-Core Intel® Xeon® Processor 5400 Series contains two cores

per die (domain) and two domains (die) per socket. BIOS will be responsible for

detecting the proper processor type and providing the number of domains to the

thermal management system. An external PECI device that is part of the thermal

management system polls the processor domains for temperature information and

currently receives the highest of the DTS output temperatures within each domain.

Figure 2-5 provides an illustration of the DTS domains for the Quad-Core Intel® Xeon®

Processor 5400 Series.

Figure 2-5. DTS Domain for Quad-Core Intel® Xeon® Processor 5400 Series