Datasheet 67

Electrical Specifications

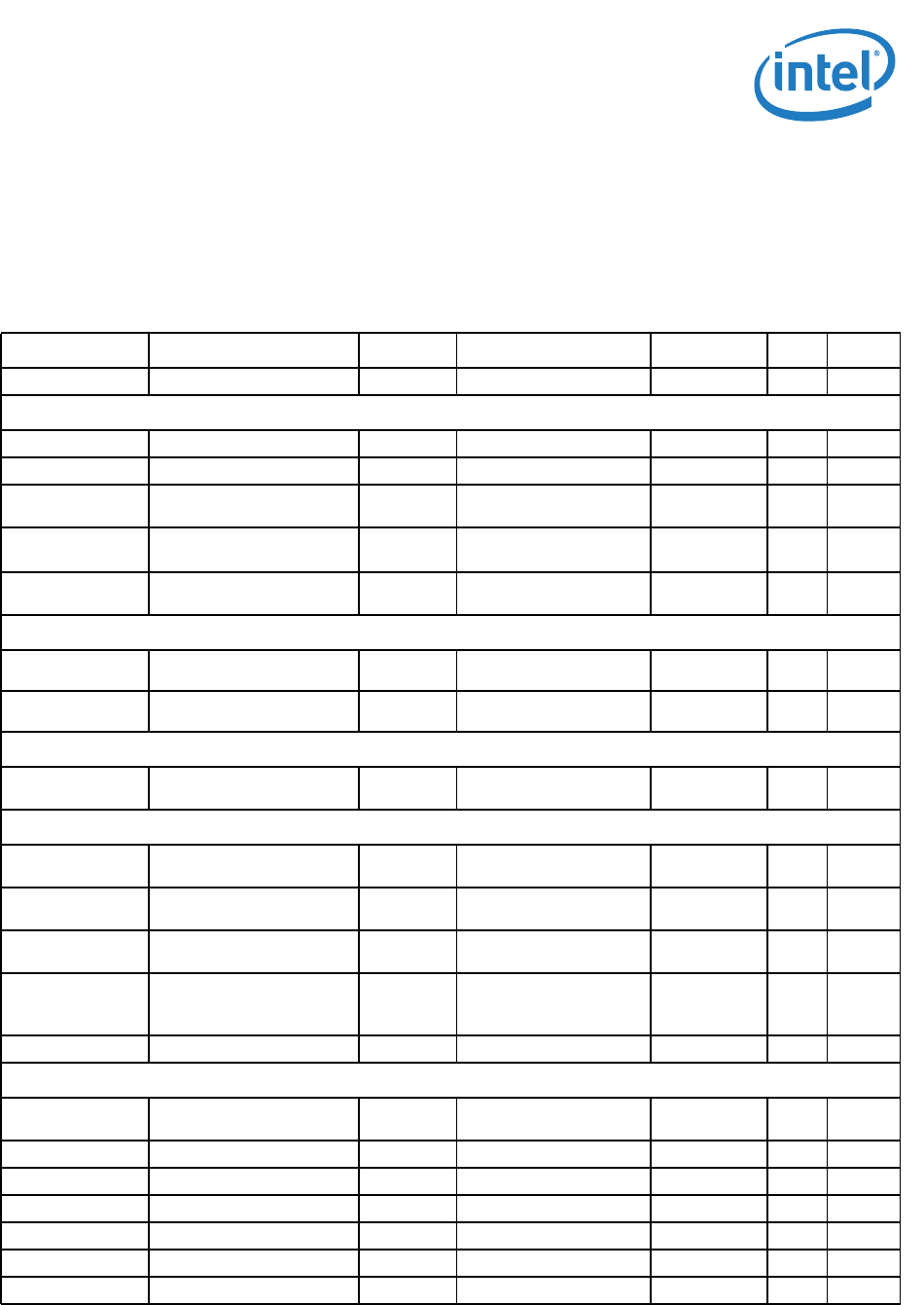

7.5.3 Signal DC Specifications

DC specifications are defined at the processor pads, unless otherwise noted.

DC specifications are only valid while meeting specifications for case temperature, clock

frequency, and input voltages. Care should be taken to read all notes associated with

each specification.

Table 7-13. DDR3 and DDR3L Signal DC Specifications (Sheet 1 of 2)

Symbol Parameter Min Typ Max Units Notes

1

I

IL

Input Leakage Current -1.4 — +1.4 mA 10

Data Signals

V

IL

Input Low Voltage — — 0.43*V

CCD

V 2, 3

V

IH

Input High Voltage 0.57*V

CCD

— — V 2, 4, 5

R

ON

DDR3 Data Buffer On

Resistance

21 — 31 6

Data ODT

On-Die Termination for Data

Signals

45

90

—

55

110

8

PAR_ERR_N ODT

On-Die Termination for

Parity Error Signals

59 — 72

Reference Clock Signals, Command, and Data Signals

V

OL

Output Low Voltage

—

(V

CCD

/ 2)* (R

ON

/(R

ON

+R

VTT_TERM

))

— V 2, 7

V

OH

Output High Voltage

—

V

CCD –

((V

CCD

/ 2)*

(R

ON

/(R

ON

+R

VTT_TERM

))

— V 2, 5, 7

Reference Clock Signal

R

ON

DDR3 Clock Buffer On

Resistance

21 — 31 6

Command Signals

R

ON

DDR3 Command Buffer On

Resistance

16 — 24 6

R

ON

DDR3 Reset Buffer On

Resistance

25 — 75 6

V

OL_CMOS1.5v

Output Low Voltage, Signals

DDR_RESET_ C{01/23}_N

— — 0.2*V

CCD

V 1, 2

V

OH_CMOS1.5v

Output High Voltage,

Signals

DDR_RESET_ C{01/23}_N

0.9*V

CCD

— — V 1, 2

I

IL_CMOS1.5v

Input Leakage Current -100 — +100 A 1, 2

Control Signals

R

ON

DDR3 Control Buffer On

Resistance

21 — 31 6

DDR01_RCOMP[0] COMP Resistance 128.7 130 131.3 9, 12

DDR01_RCOMP[1] COMP Resistance 25.839 26.1 26.361 9, 12

DDR01_RCOMP[2] COMP Resistance 198 200 202 9, 12

DDR23_RCOMP[0] COMP Resistance 128.7 130 131.3 9, 12

DDR23_RCOMP[1] COMP Resistance 25.839 26.1 26.361 9, 12

DDR23_RCOMP[2] COMP Resistance 198 200 202 9, 12