Interfaces

26 Datasheet, Volume 1

2.1.3.2.1 Dual-Channel Symmetric Mode

Dual-Channel Symmetric mode, also known as interleaved mode, provides maximum

performance on real world applications. Addresses are ping-ponged between the

channels after each cache line (64-byte boundary). If there are two requests, and the

second request is to an address on the opposite channel from the first, that request can

be sent before data from the first request has returned. If two consecutive cache lines

are requested, both may be retrieved simultaneously, since they are ensured to be on

opposite channels. Use Dual-Channel Symmetric mode when both Channel A and

Channel B DIMM connectors are populated in any order, with the total amount of

memory in each channel being the same.

When both channels are populated with the same memory capacity and the boundary

between the dual channel zone and the single channel zone is the top of memory, the

IMC operates completely in Dual-Channel Symmetric mode.

Note: The DRAM device technology and width may vary from one channel to the other.

2.1.4 Rules for Populating Memory Slots

In all System Memory Organization Modes, the frequency and latency timings of the

system memory is the lowest supported frequency and slowest supported latency

timings of all memory DIMM modules placed in the system, as determined through the

SPD registers.

Note: In a Two DIMM Per Channel (2DPC) daisy chain layout memory configuration, the

furthest DIMM from the processor of any given channel must always be populated first.

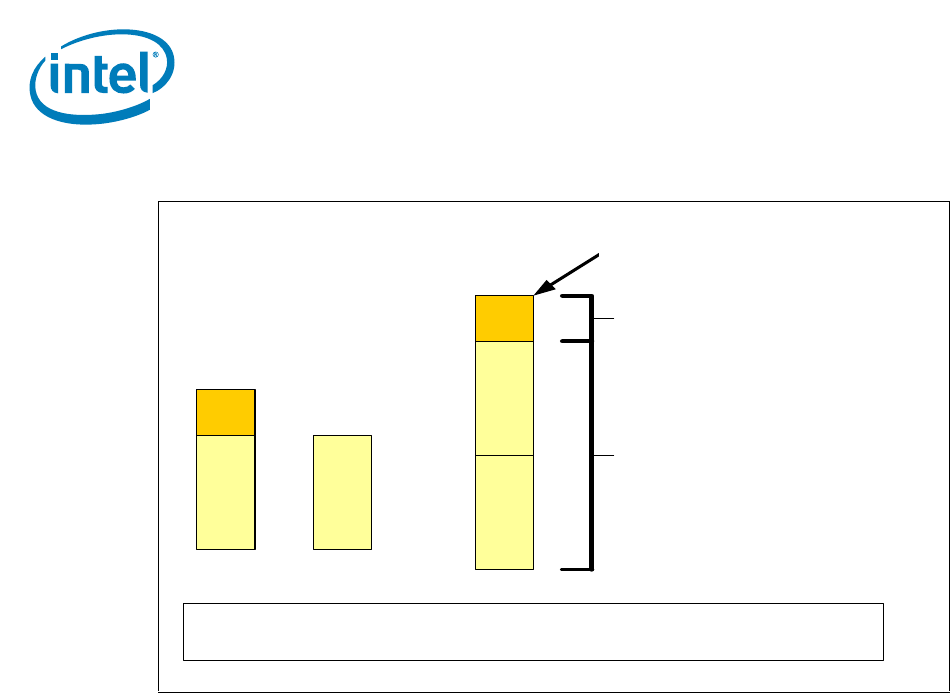

Figure 2-1. Intel

®

Flex Memory Technology Operation

CH BCH A

B B

C

B

B

C

Non interleaved

access

Dual channel

interleaved access

TOM

CH A and CH B can be configured to be physical channels 0 or 1

B – The largest physical memory amount of the smaller size memory module

C – The remaining physical memory amount of the larger size memory module