Datasheet, Volume 1 33

Interfaces

2.4 Processor Graphics Controller (GT)

New Graphics Engine Architecture includes 3D compute elements, Multi-format

hardware assisted decode/encode pipeline, and Mid-Level Cache (MLC) for superior

high definition playback, video quality, and improved 3D performance and Media.

The Display Engine handles delivering the pixels to the screen, and is the primary

channel interface for display memory accesses and “PCI-like” traffic in and out.

2.4.1 3D and Video Engines for Graphics Processing

The 3D graphics pipeline architecture simultaneously operates on different primitives or

on different portions of the same primitive. All the cores are fully programmable,

increasing the versatility of the 3D Engine. The Gen 7.0 3D engine provides the

following performance and power-management enhancements:

• Up to 16 Execution units (EUs)

•Hierarchal-Z

• Video quality enhancements

2.4.1.1 3D Engine Execution Units

• Supports up to 16 EUs. The EUs perform 128-bit wide execution per clock

• Support SIMD8 instructions for vertex processing and SIMD16 instructions for pixel

processing

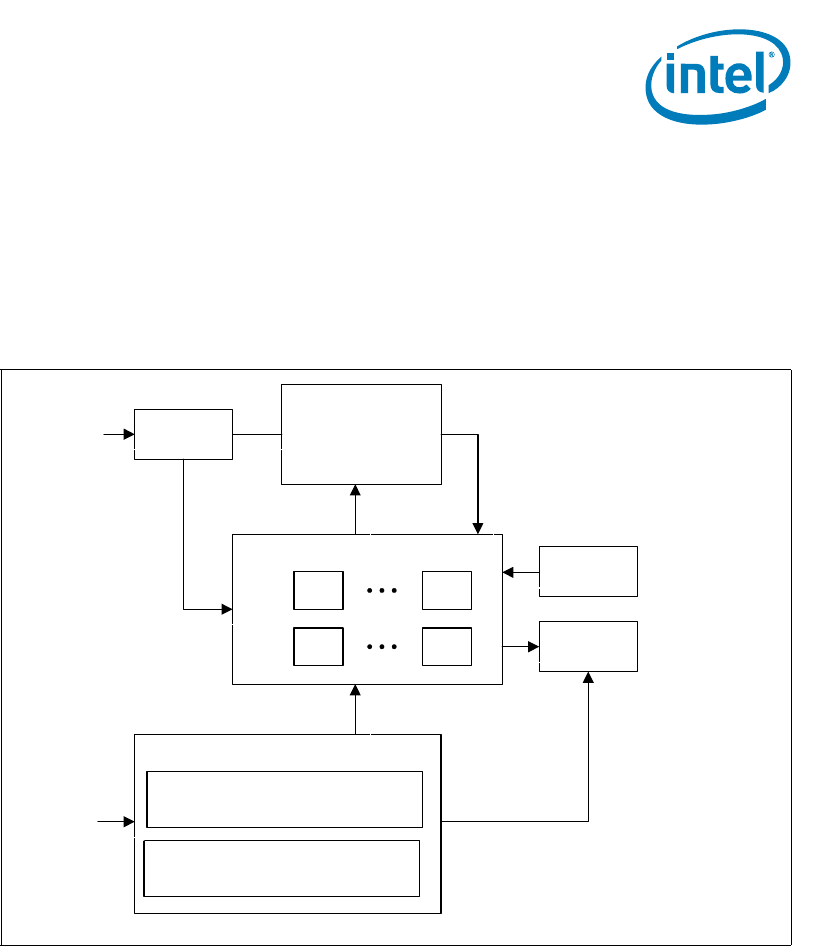

Figure 2-6. Processor Graphics Controller Unit Block Diagram

Vertex

Fetch

VS/GS

Setup/Rasterize

Hierachical Z

Hardware Clipper

EU EU

EU EU

Unified Execution Unit Array

Texture

Unit

Pixel

Backend

Full MPEG2, VC1, AVC Decode

Fixed Function Post Processing

Full AVC Encode

Partial MPEG2, VC1 Encode

Multi-Format Decode/Encode

Additional Post Processing