TIMER 1 S3C9228/P9228

11-6

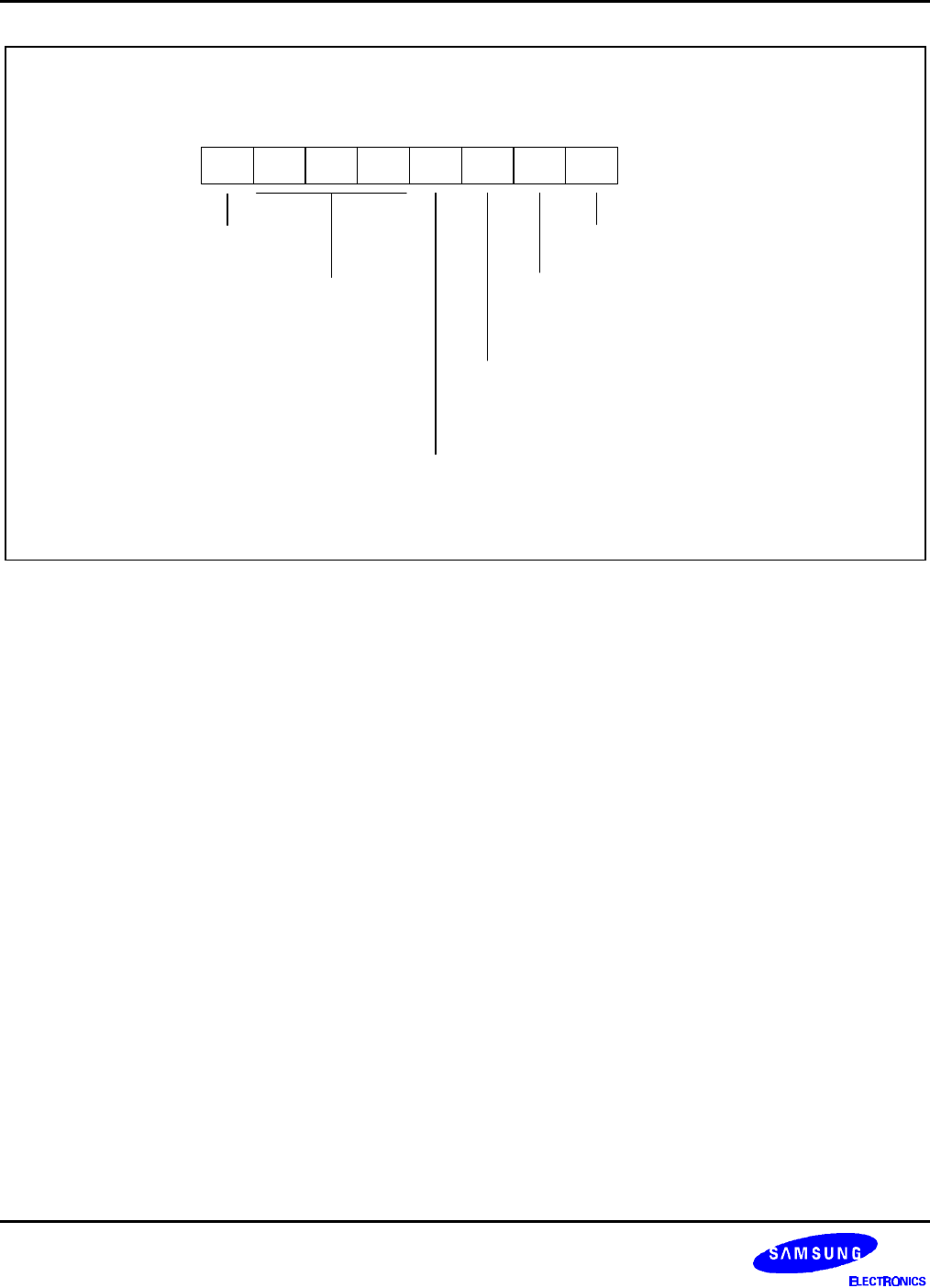

Timer B Control Register (TBCON)

BAH, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Timer B match interrupt enable bit:

0 = Disable match interrupt

1 = Enable match interrupt

Not used

Timer B count enable bit:

0 = Disable counting operating

1 = Enable counting operating

Timer B counter clear bit:

0 = No effect

1 = Clear the timer B counter (when write)

Timer B clock selection bits:

000 = fxx/512

001 = fxx/256

010 = fxx/64

011 = fxx/8

100 = fxx (system clock)

101 = fxt (sub clock)

110 = Not available

111 = Not available

Not used

Figure 11-4. Timer B Control Register (TBCON)