BIOS Setup Utility SY-5STM

51

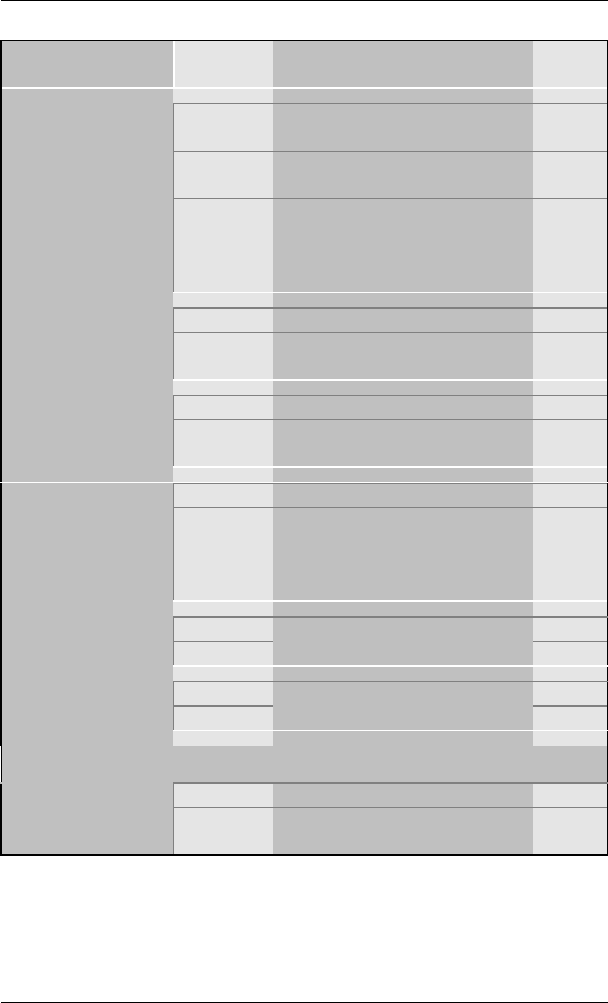

CHIPSET FEATURES SETUP (Continued)

CHIPSET

FEATURES

Setting Description Note

PCILK/4 The ISA bus runs on PCI

Bus Clock divided by 4.

Default

PCILK/3 The ISA bus runs on PCI

Bus Clock divided by 3.

ISA Bus Clock

Frequency

7.159MHz ISA bus clock fixed to

7.159MHz when [Auto

Configuration] field is set to

[Enabled].

Read-

Only

Disabled

System BIOS

Cacheable

Enabled The ROM area F0000H-

FFFFFH is cacheable.

Default

Disabled

Video BIOS

Cacheable

Enabled The video BIOS C0000H-

C7FFFH is cacheable.

Default

Disabled Default

Memory Hole At

15M-16M

Enabled Some interface cards will

map their ROM address to

this area. If this occurs,

select [Enabled] in this field.

1 MB Default

VGA Shared

Memory Size

0.5-4 MB

VGA memory size shared

with system memory.

40 Default

VGA Memory

Clock (MHz)

40-70 MHz

Selects the frequency of the

VGA memory clock.

The following field applies to Cyrix type of CPUs only.

Disabled Default

Linear Mode

SRAM Support

Enabled Linear mode SRAM support

for Cyrix type of CPU.