XLi IEEE 1588 Clock 7

997-01510-03, Rev. C, 12/12/2006

2

5

1

SSSSSSSSSSSS SSSSSSSSSS SSSSSSS S SSS S SSSSS S

Clock Architecture

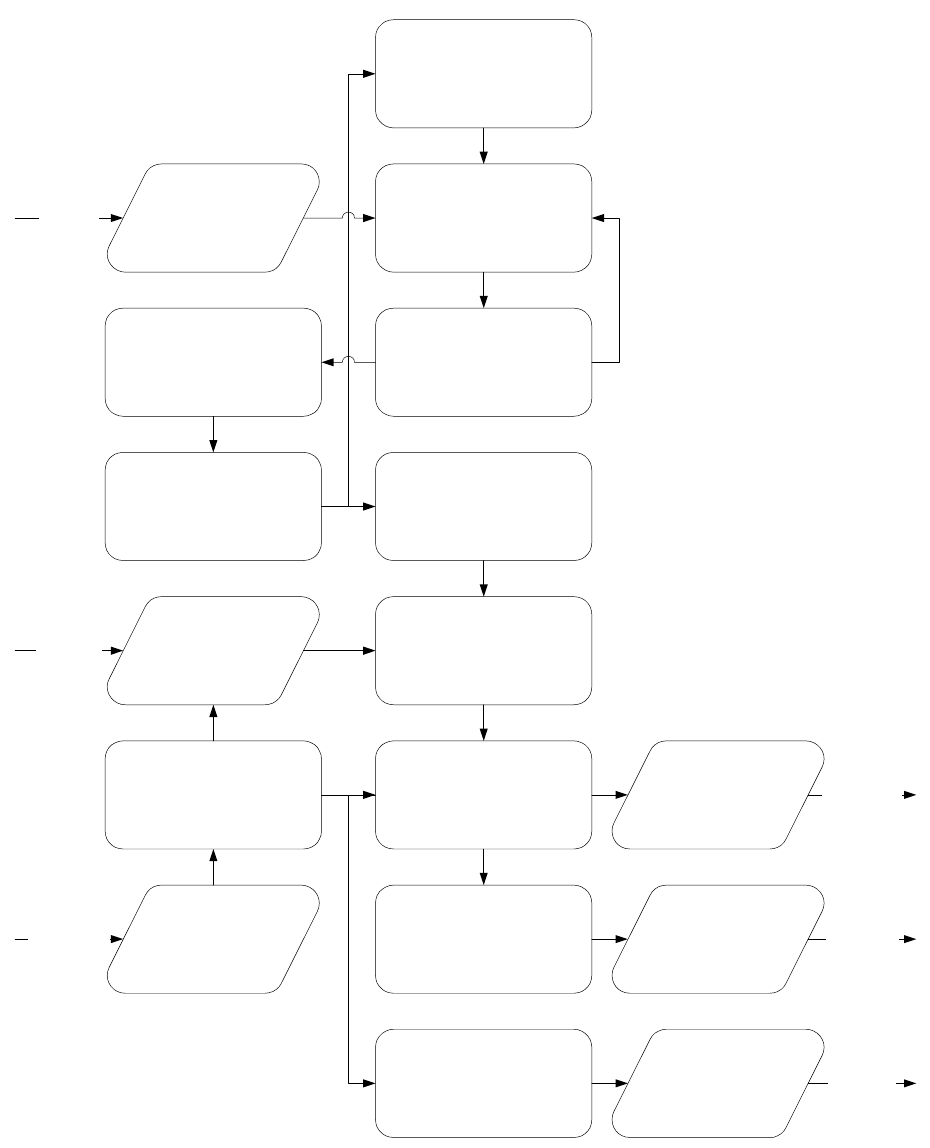

Figures 1 and 2 on the following pages provide a simplified view of the standard XLi's clock architecture.

Figure 1: Functional Timing Block Diagram

DAC

16.384 MHz Osc. PLL

Rate Gen

Code Generation

Clock Machine

Phase Compare

200 MHz PLL

Clock DPLL

Aux Ref

1,5,10 MHz

Phase Measurement

10 MHz Osc.

1 PPS

Timing

Select

Time and Clock

Recovery

Code Input

1 PPS

Output

Code Out

Rate Out

Code Input

1 PPS A

1PPS B

Aux Ref

1 PPS Out

Code Out

Rate Out