Simulation

XAPP979 (v1.0) February 26, 2007 www.xilinx.com 30

R

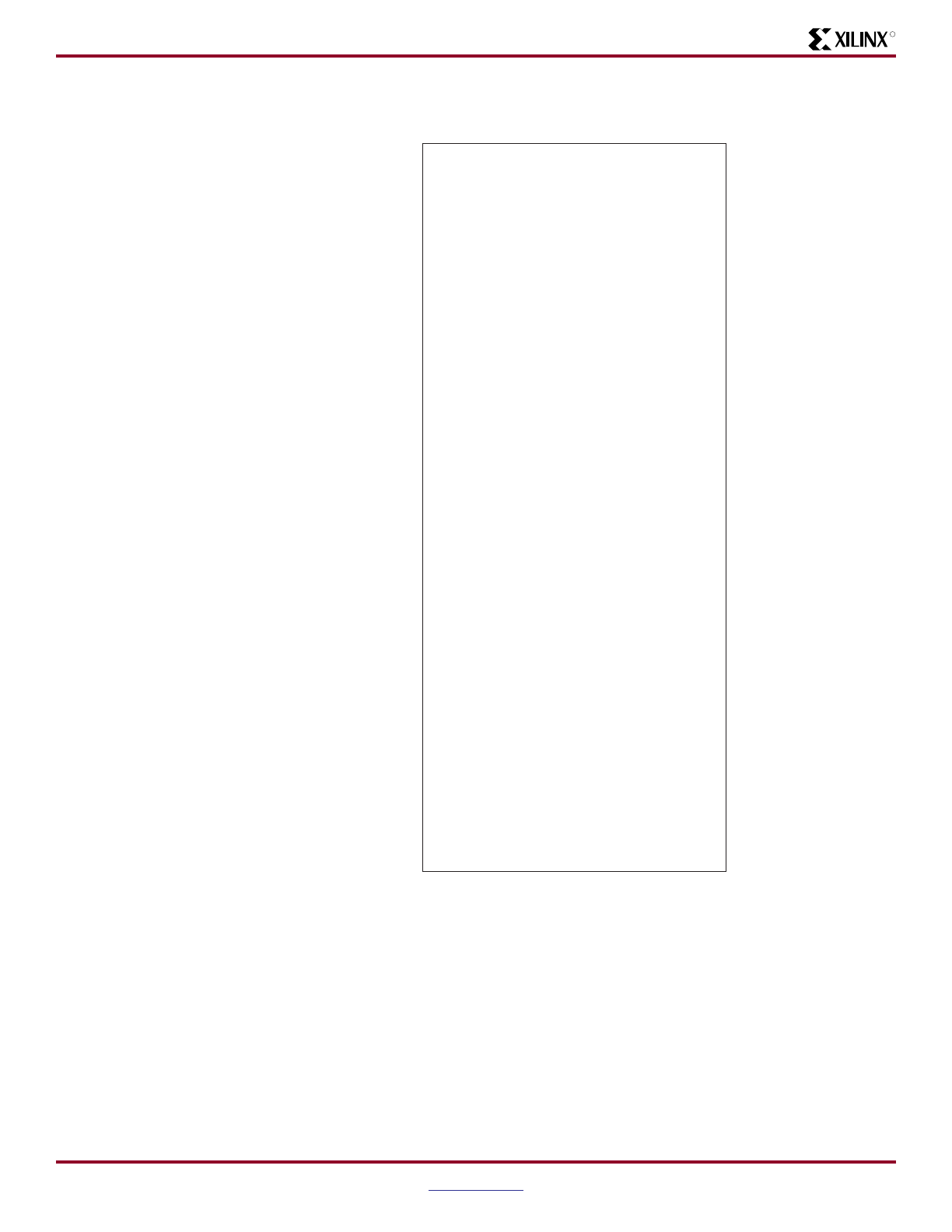

Figure 33 provides the test code used in the simulation with the OPB IIC with the AA address

as the master.

Figure 33: Test code with iic_AA as Master

write CR_20 0x40 -- GC, En

write ADR_20 0x20 - Sets address as 0x20

write CR_AA 0x01 - Enable

write ADR_AA 0xAA

write RC_FIFO_PIRQ_AA 0x0

write IER_AA 0x04 -- Enable DTRE interrupt

write RC_FIFO_PIRQ 0x01 (473 us)

write DTR_20 0x3C

write DTR_20 0x55

write DTR_AA 0x0 -- Genera l Call

write CR_AA 0x0D -- RSTA, TxAK, TX, MSMS, Enable

wait_for_intr

read SR_AA 0xC4 -- TFE, RFE, BB

read ISR_AA 0xD4 -- TFHE, DTRE

write CR_AA 0x35 RSTA , M S, EN (547 us)

write DTR_AA 0x21

write DTR_AA 0xFF

write IER_AA 0x08

wait_for_intr -- waiting for DRR_AA full

read SR_AA 0x0C -- SRW, BB (678 us)

write CR_AA 0x37 -- Clear FIFO

write CR_AA 0x35

read DRR_AA 0x3C

write ISR_AA 0xC*

write DTR_AA 0x21

wait_for_intr

read SR_AA 0x8C

read ISR_AA 0xCA -- TXER, DFF Full

write CR_AA 0x41

read DRR_AA 0x55 (787 us)

write ISR_AA 0xC8

write IRE_AA 0x10 -- Enable Bus is not Busy

wait_for_intr

X979_33_012907