CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 21 of 68

12. Clocking

The enCoRe II LV has two internal oscillators, the internal 24

MHz oscillator and the 32 kHz low power oscillator.

The internal 24 MHz oscillator is designed such that it is trimmed

to an output frequency of 24 MHz over temperature and voltage

variation. The internal 24 MHz oscillator accuracy is 24 MHz

–22% to +10% (between 0° and 70°C). No external components

are required to achieve this level of accuracy.

Firmware is responsible for selecting the correct trim values from

the user row to match the power supply voltage in the end appli-

cation and writing the values to the trim registers IOSCTR and

LPOSCTR.

The internal low speed oscillator of nominally 32 kHz provides a

slow clock source for the enCoRe II LV in suspend mode, partic-

ularly to generate a periodic wakeup interrupt and also to provide

a clock to sequential logic during power up and power down

events when the main clock is stopped. In addition, this oscillator

can be used as a clocking source for the Interval Timer clock

(ITMRCLK) and Capture Timer clock (TCAPCLK). The 32 kHz

low power oscillator can operate in low power mode or provide a

more accurate clock in normal mode. The internal 32 kHz low

power oscillator accuracy ranges from –53.12% to +56.25%. The

32 kHz low power oscillator can be calibrated against the internal

24 MHz oscillator or another timing source, if desired.

enCoRe II LV provides the ability to load new trim values for the

24 MHz oscillator based on voltage. This allows Vdd to be

monitored and have firmware trim the oscillator based on voltage

present. The IOSCTR register is used to set trim values for the

24 MHz oscillator. enCoRe II LV is initialized with 3.30V trim

values at power on, then firmware is responsible for transferring

the correct set of trim values to the trim registers to match the

application’s actual Vdd. The 32 kHz oscillator generally does

not require trim adjustments for voltage but trim values for the 32

kHz are also stored in Supervisory ROM.

To improve the accuracy of the IMO, new trim values are loaded

based on supply voltage to the part. For this, firmware needs to

make modifications to two registers:

1. The internal oscillator trim register at location 0x34.

2. The gain register at location 0x38.

12.1 Trim Values for the IOSCTR Register

The trim values are stored in SROM tables in the part as shown

in Figure 11-3.

The trim values are read out from the part based on voltage

settings and written to the IOSCTR register at location 0x34. The

following pseudo code shows how this is done.

_main:

mov A, 2

mov [SSC_BLOCKID], A

Call SROM operation to read the SROM table (Refer to section

SROM Table Read Description on page 19)

//After this command is executed, the trim

//values for 3.3, 3.0, 2.85 and 2.7 are stored

//at locations FC through FF in the RAM. SROM

//calls are explained in the previous section of

//this data sheet

; mov A, [FCh] // trim values for 3.3V

mov A, [FDh] // trim values for 3.0V

; mov A, [FEh] // trim values for 2.85V

; mov A, [FFh] // trim values for 2.70V

mov reg[IOSCTR],A // Loading IOSCTR with

// trim values for

// 3.0V

.terminate:

jmp .terminate

Gain value for the register at location [0x38]:

3.3V = 0x40

3.0V = 0x40

2.85V = 0xFF

2.70V = 0xFF

Load register [0x38] with the gain values corresponding to the

appropriate voltage.

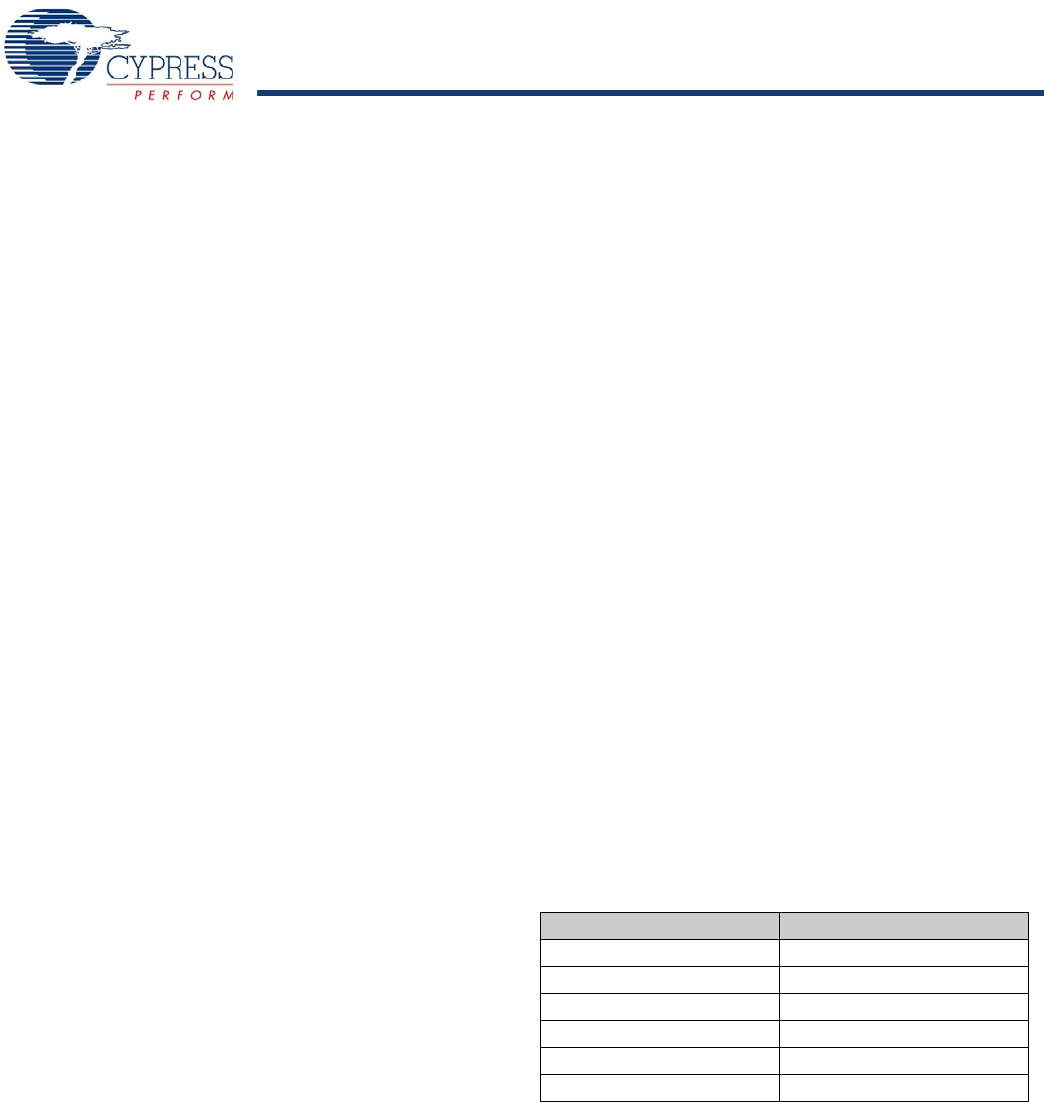

Table 12-1. Oscillator Trim Values vs. Voltage Settings

Supervisory ROM Table Function

Table2 FCh 24 MHz IOSCTR at 3.30V

Table2 FDh 24 MHz IOSCTR at 3.00V

Table2 FEh 24 MHz IOSCTR at 2.85V

Table2 FFh 24 MHz IOSCTR at 2.70V

Table3 F8h 32 kHz LPOSCTR at 3.30V

Table3 F9h 32 kHz LPOSCTR at 3.00V

[+] Feedback [+] Feedback