CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 57 of 68

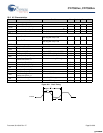

Table 19-6. Interrupt Mask 2 (INT_MSK2) [0xDF] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field Reserved GPIO Port 4

Int Enable

GPIO Port 3

Int Enable

GPIO Port 2

Int Enable

Reserved INT2

Int Enable

16-bit Counter

Wrap Int Enable

TCAP1

Int Enable

Read/Write – R/W R/W R/W –R/WR/W R/W

Default 0 0 0 0 000 0

Bit 7: Reserved

Bit 6: GPIO Port 4 Interrupt Enable

0 = Mask GPIO Port 4 interrupt

1 = Unmask GPIO Port 4 interrupt

Bit 5: GPIO Port 3 Interrupt Enable

0 = Mask GPIO Port 3 interrupt

1 = Unmask GPIO Port 3 interrupt

Bit 4: GPIO Port 2 Interrupt Enable

0 = Mask GPIO Port 2 interrupt

1 = Unmask GPIO Port 2 interrupt

Bit 3: Reserved

Bit 2: INT2 Interrupt Enable

0 = Mask INT2 interrupt

1 = Unmask INT2 interrupt

Bit 1: 16-bit Counter Wrap Interrupt Enable

0 = Mask 16-bit Counter Wrap interrupt

1 = Unmask 16-bit Counter Wrap interrupt

Bit 0: TCAP1 Interrupt Enable

0 = Mask TCAP1 interrupt

1 = Unmask TCAP1 interrupt

The GPIO interrupts are edge-triggered.

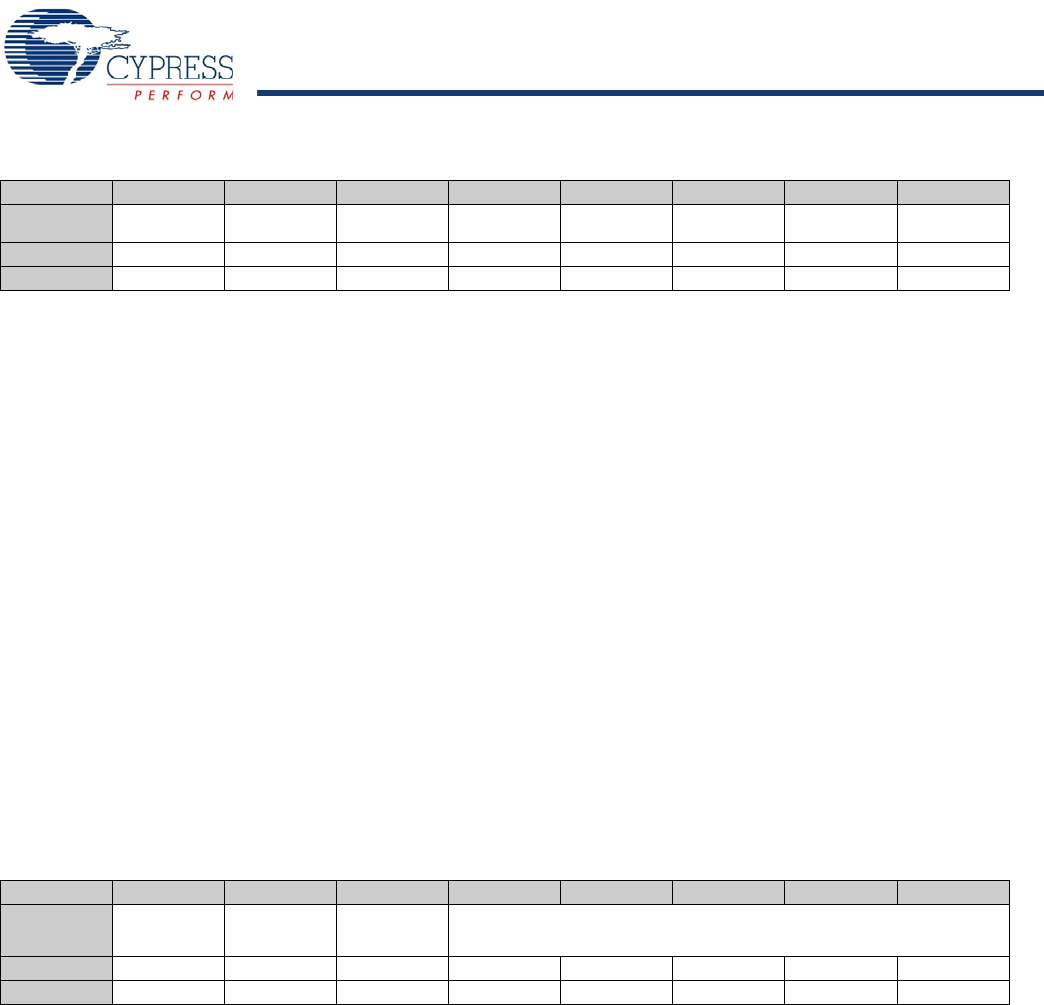

Table 19-7. Interrupt Mask 1 (INT_MSK1) [0xE1] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field TCAP0

Int Enable

Prog Interval

Timer

Int Enable

1-ms Timer

Int Enable

Reserved

Read/Write R/W R/W R/W – ––– –

Default 0 0 0 0 000 0

Bit 7: TCAP0 Interrupt Enable

0 = Mask TCAP0 interrupt

1 = Unmask TCAP0 interrupt

Bit 6: Prog Interval Timer Interrupt Enable

0 = Mask Prog Interval Timer interrupt

1 = Unmask Prog Interval Timer interrupt

Bit 5: 1 ms Timer Interrupt Enable

0 = Mask 1 ms interrupt

1 = Unmask 1 ms interrupt

Bit [4:0]: Reserved

[+] Feedback [+] Feedback