CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 25 of 68

12.2.2 Interval Timer Clock (ITMRCLK)

The Interval Timer Clock (ITMRCLK) is sourced from the external

crystal oscillator, the internal 24 MHz oscillator, the internal 32

kHz low power oscillator, or the Timer Capture clock. A program-

mable prescaler of 1, 2, 3, or 4 then divides the selected source.

The 12-bit Programmable Interval Timer is a simple down

counter with a programmable reload value. It provides a 1 μs

resolution by default. When the down counter reaches zero, the

next clock is spent reloading. The reload value is read and

written when the counter is running, but ensure that the counter

does not unintentionally reload when the 12-bit reload value is

only partially stored—between two writes of the 12-bit value. The

programmable interval timer generates an interrupt to the CPU

on each reload.

The parameters to be set shows up on the device editor view of

PSoC Designer when you place the enCoRe II LV timer user

module. The parameters are PITIMER_Source and

PITIMER_Divider. The PITIMER_Source is the clock to the timer

and the PITIMER_Divider is the value the clock is divided by.

The interval register (PITMR) holds the value that is loaded into

the PIT counter on terminal count.

The programmable interval timer resolution is configurable. For

example:

TCAPCLK divide by x of CPU clock (for example TCAPCLK

divide by 2 of a 24 MHz CPU clock gives a frequency of 12 MHz)

ITMRCLK divide by x of TCAPCLK (for example, ITMRCLK

divide by 3 of TCAPCLK is 4 MHz so resolution is 0.25 μs)

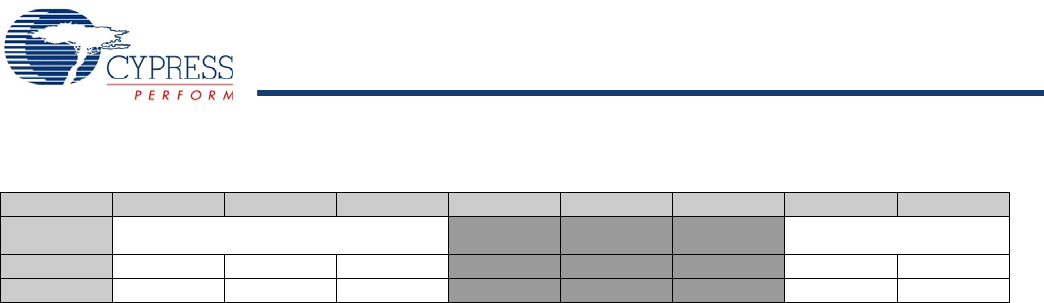

Table 12-4. Clock IO Configuration (CLKIOCR) [0x32] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field

Reserved

XOSC

Select

XOSC

Enable

EFTB

Disabled

CLKOUT Select

Read/Write – – – R/W R/W R/W R/W R/W

Default 0 0 0 0 0 0 0 0

Bit [7:5]: Reserved

Bit 4: XOSC Select

This bit, when set, selects the external crystal oscillator clock as clock source of external clock. When selecting the crystal

oscillator clock, first enable the crystal oscillator and wait for few cycles. This is the oscillator stabilization period. Then select

the crystal clock as clock source. Similarly, to deselect crystal clock, first deselect crystal clock as clock source then disable the

crystal oscillator.

0 = Not select external crystal oscillator clock.

1 = Select the external crystal oscillator clock.

Bit 3: XOSC Enable

This bit is only available on the CY7C601xx.

This bit when set enables the external crystal oscillator. The external crystal oscillator shares pads CLKIN and CLKOUT with

two GPIOs—P0.0 and P0.1 respectively. When the external crystal oscillator is enabled, the CLKIN signal comes from the

external crystal oscillator block and the output enables on the GPIOs for P0.0 and P0.1 are disabled, eliminating the possibility

of contention. When the external crystal oscillator is disabled, the source for CLKIN signal comes from the P0.0 GPIO input.

0 = Disable the external oscillator.

1 = Enable the external oscillator.

Note The external crystal oscillator startup time takes up to 2 ms.

Bit 2: EFTB Disabled

This bit is only available on the CY7C601xx.

0 = Enable the EFTB filter.

1 = Disable the EFTB filter, causing CLKIN to bypass the EFTB filter.

Bit [1:0]: CLKOUT Select

0 0 = Internal 24 MHz Oscillator

0 1 = External oscillator source

1 0 = Internal 32 kHz low power oscillator

1 1 = CPUCLK

[+] Feedback [+] Feedback