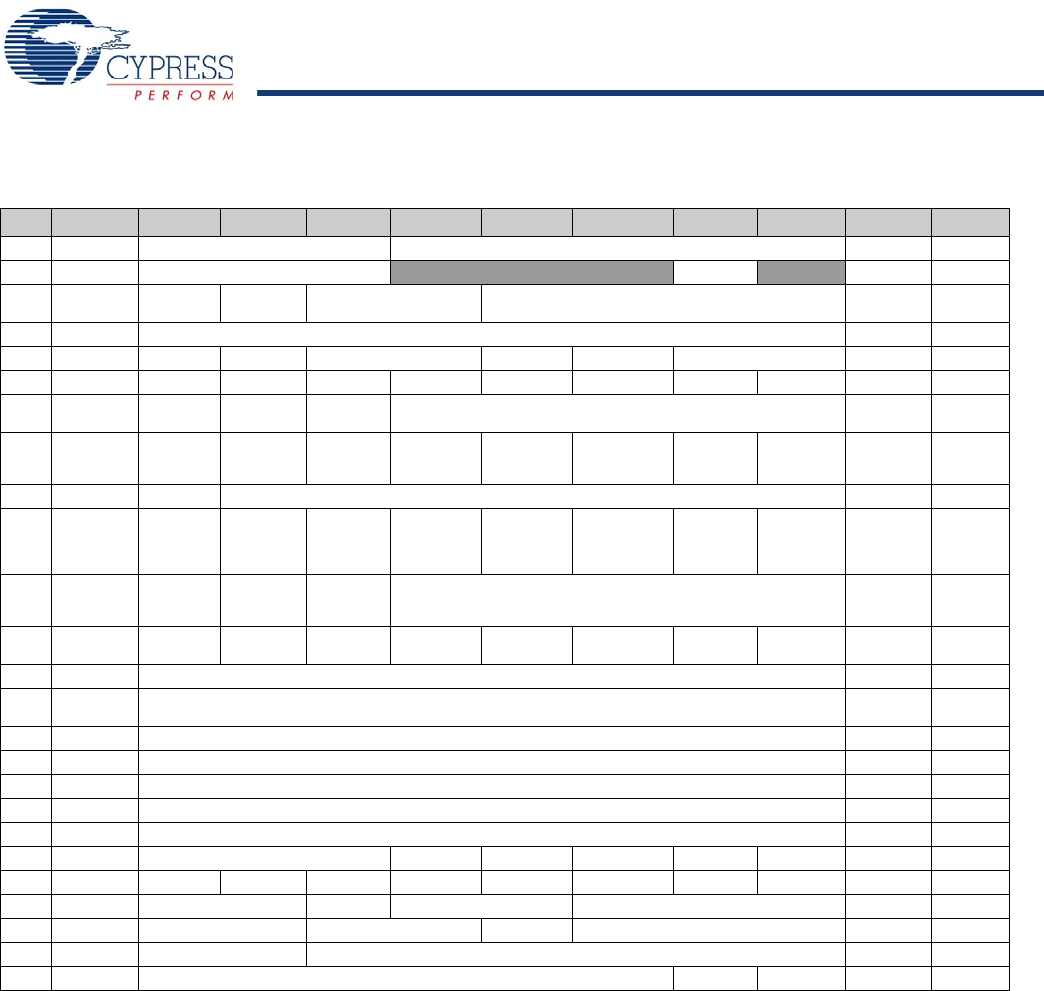

CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 7 of 68

Note In the R/W column:

b = Both Read and Write

r = Read Only

w = Write Only

c = Read or Clear

d = Calibration Value. Must not change during normal use

34 IOSCTR foffset[2:0] Gain[4:0] bbbbbbbb 000ddddd

35 XOSCTR Reserved

XOSC XGM [2:0] Reserved Mode ---bbb-b 000ddddd

36 LPOSCTR 32 kHz Low

Power

Reserved 32 kHz Bias Trim [1:0] 32 kHz Freq Trim [3:0] b-bbbbbb d-dddddd

3C SPIDATA SPIData[7:0] bbbbbbbb 00000000

3D SPICR Swap LSB First Comm Mode CPOL CPHA SCLK Select bbbbbbbb 00000000

DA INT_CLR0 GPIO Port 1 Sleep Timer INT1 GPIO Port 0 SPI Receive SPI Transmit INT0 POR/LVD bbbbbbbb 00000000

DB INT_CLR1 TCAP0 Prog Interval

Timer

1 ms Timer Reserved bbb----- 00000000

DC INT_CLR2 Reserved GPIO Port 4 GPIO Port 3 GPIO Port 2 Reserved INT2 16-bit

Counter

Wrap

TCAP1 -bbb-bbb 00000000

DE INT_MSK3 ENSWINT Reserved r------- 00000000

DF INT_MSK2 Reserved GPIO Port 4

Int Enable

GPIO Port 3

Int Enable

GPIO Port 2

Int Enable

Reserved INT2

Int Enable

16-bit

Counter

Wrap Int

Enable

TCAP1

Int Enable

-bbb-bbb 00000000

E1 INT_MSK1 TCAP0

Int Enable

Prog Interval

Timer

Int Enable

1 ms Timer

Int Enable

Reserved bbb----- 00000000

E0 INT_MSK0 GPIO Port 1

Int Enable

Sleep Timer

Int Enable

INT1

Int Enable

GPIO Port 0

Int Enable

SPI Receive

Int Enable

SPI Transmit

Int Enable

INT0

Int Enable

POR/LVD

Int Enable

bbbbbbbb 00000000

E2 INT_VC Pending Interrupt [7:0] bbbbbbbb 00000000

E3 RESWDT Reset Watchdog Timer [7:0] wwwwwww

w

00000000

-- CPU_A Temporary Register T1 [7:0] -------- 00000000

-- CPU_X X[7:0] -------- 00000000

-- CPU_PCL Program Counter [7:0] -------- 00000000

-- CPU_PCH Program Counter [15:8] -------- 00000000

-- CPU_SP Stack Pointer [7:0] -------- 00000000

F7 CPU_F Reserved XIO Super Carry Zero Global IE ---brbbb 00000010

FF CPU_SCR GIES Reserved WDRS PORS Sleep Reserved Reserved Stop r-ccb--b 00010100

1E0 OSC_CR0 Reserved No Buzz Sleep Timer [1:0] CPU Speed [2:0] --bbbbbb 00000000

1E3 LVDCR Reserved PORLEV[1:0] Reserved VM[2:0] --bb-bbb 00000000

1EB ECO_TR Sleep Duty Cycle [1:0] Reserved bb------ 00000000

1E4 VLTCMP Reserved LVD PPOR ------rr 00000000

Table 7-1. enCoRe II LV Register Summary (continued)

The XIO bit in the CPU Flags Register must be set to access the extended register space for all registers above 0xFF.

Addr Name 7 6 5 4 3 2 1 0 R/W Default

[+] Feedback [+] Feedback