CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 29 of 68

12.2.6 LPOSC Trim

12.3 CPU Clock During Sleep Mode

When the CPU enters sleep mode the CPUCLK Select (Bit 0, Table 12-2) is forced to the internal oscillator, and the oscillator is

stopped. When the CPU comes out of sleep mode it runs on the internal oscillator. The internal oscillator recovery time is three

clock cycles of the internal 32 kHz low power oscillator.

If the system requires the CPU to run off the external clock after waking from sleep mode, firmware needs to switch the clock

source for the CPU. If the external clock source is the external oscillator and the oscillator is disabled, firmware needs to enable

the external oscillator, wait for it to stabilize, and then change the clock source.

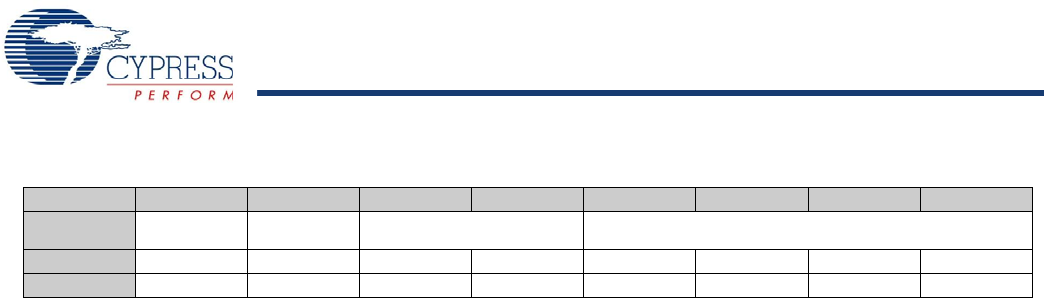

Table 12-8. LPOSC Trim (LPOSCTR) [0x36] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field 32 kHz Low

Power

Reserved 32 kHz Bias Trim [1:0] 32 kHz Freq Trim [3:0]

Read/Write R/W – R/W R/W R/W R/W R/W R/W

Default 0 – D D DDD D

This register is used to calibrate the 32 kHz low speed oscillator. The reset value is undefined but during boot the SROM writes

a calibration value that is determined during manufacturing test. This is the meaning of ‘D’ in the Default field. The trim value is

adjusted vs. voltage as noted in Table 12-2.

Bit 7: 32 kHz Low Power

0 = The 32 kHz low speed oscillator operates in normal mode.

1 = The 32 kHz low speed oscillator operates in a low power mode. The oscillator continues to function normally but with reduced

accuracy.

Bit 6: Reserved

Bit [5:4]: 32 kHz Bias Trim [1:0]

These bits control the bias current of the low power oscillator.

0 0 = Mid bias

0 1 = High bias

1 0 = Reserved

1 1 = Reserved

Note Do not program the 32 kHz Bias Trim [1:0] field with the reserved 10b value as the oscillator does not oscillate at all corner

conditions with this setting.

Bit [3:0]: 32 kHz Freq Trim [3:0]

These bits are used to trim the frequency of the low power oscillator.

[+] Feedback [+] Feedback