CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 6 of 68

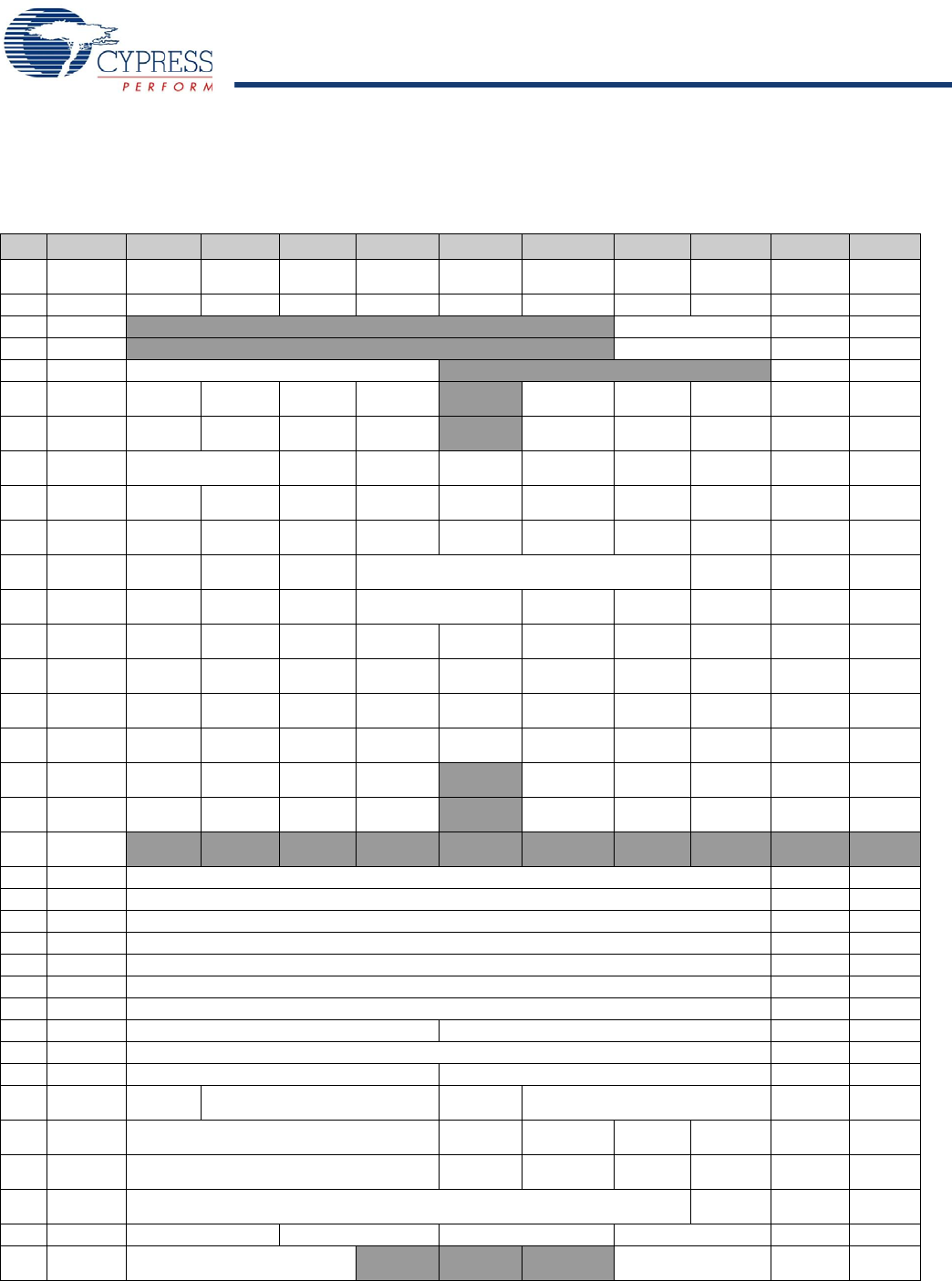

7. Register Summary

Table 7-1. enCoRe II LV Register Summary

The XIO bit in the CPU Flags Register must be set to access the extended register space for all registers above 0xFF.

Addr Name 7 6 5 4 3 2 1 0 R/W Default

00 P0DATA P0.7 P0.6/TIO1 P0.5/TIO0 P0.4/INT2 P0.3/INT1 P0.2/INT0 P0.1/

CLKOUT

P0.0/CLKIN bbbbbbbb 00000000

01 P1DATA P1.7 P1.6/SMISO P1.5/SMOSI P1.4/SCLK P1.3/SSEL P1.2 P1.1 P1.0 bbbbbbbb 00000000

02 P2DATA

P2.7–P2.2 P2.1–P2.0 bbbbbbbb 00000000

03 P3DATA

P3.7–P3.2 P3.1–P3.0 bbbbbbbb 00000000

04 P4DATA Reserved

P4.3–P4.0 ----bbbb 00000000

05 P00CR Reserved Int Enable Int Act Low TTL Thresh

High Sink Open Drain Pull up

Enable

Output

Enable

-bbbbbbb 00000000

06 P01CR CLK Output Int Enable Int Act Low TTL Thresh

High Sink Open Drain Pull Up

Enable

Output

Enable

bbbbbbbb 00000000

07–09 P02CR–

P04CR

Reserved Int Act Low TTL Thresh Reserved Open Drain Pull Up

Enable

Output

Enable

--bb-bbb 00000000

0A–0B P05CR–

P06CR

TIO Output Int Enable Int Act Low TTL Thresh Reserved Open Drain Pull Up

Enable

Output

Enable

bbbb-bbb 00000000

0C P07CR Reserved Int Enable Int Act Low TTL Thresh Reserved Open Drain Pull Up

Enable

Output

Enable

-bbb-bbb 00000000

0D P10CR Reserved Int Enable Int Act Low Reserved Output

Enable

-bb----b 00000000

0E P11CR Reserved Int Enable Int Act Low Reserved Open Drain Reserved Output

Enable

-bb--b-b 00000000

0F P12CR CLK Output Int Enable Int Act Low TTL

Threshold

Reserved Open Drain Pull Up

Enable

Output

Enable

bbbb-bbb 00000000

10 P13CR Reserved Int Enable Int Act Low Reserved High Sink Open Drain Pull Up

Enable

Output

Enable

-bb-bbbb 00000000

11–13 P14CR–

P16CR

SPI Use Int Enable Int Act Low Reserved High Sink Open Drain Pull Up

Enable

Output

Enable

bbb-bbbb 00000000

14 P17CR Reserved Int Enable Int Act Low Reserved High Sink Open Drain Pull Up

Enable

Output

Enable

-bb-bbbb 00000000

15 P2CR Reserved Int Enable Int Act Low TTL Thresh

High Sink Open Drain Pull Up

Enable

Output

Enable

-bbbbbbb 00000000

16 P3CR Reserved Int Enable Int Act Low TTL Thresh

High Sink Open Drain Pull Up

Enable

Output

Enable

-bbbbbbb 00000000

17 P4CR

Reserved Int Enable Int Act Low TTL Thresh Reserved Open Drain Pull Up

Enable

Output

Enable

-bbb-bbb 00000000

20 FRTMRL Free Running Timer [7:0] bbbbbbbb 00000000

21 FRTMRH Free Running Timer [15:8] bbbbbbbb 00000000

22 TCAP0R Capture 0 Rising [7:0] rrrrrrrr 00000000

23 TCAP1R Capture 1 Rising [7:0] rrrrrrrr 00000000

24 TCAP0F Capture 0 Falling [7:0] rrrrrrrr 00000000

25 TCAP1F Capture 1 Falling [7:0] rrrrrrrr 00000000

26 PITMRL Prog Interval Timer [7:0] rrrrrrrr 00000000

27 PITMRH Reserved Prog Interval Timer [11:8] ----rrrr 00000000

28 PIRL Prog Interval [7:0] bbbbbbbb 00000000

29 PIRH Reserved Prog Interval [11:8] ----bbbb 00000000

2A TMRCR First Edge

Hold

8-bit Capture Prescale Cap0 16-bit

Enable

Reserved bbbbb--- 00000000

2B TCAPINTE Reserved Cap1 Fall

Active

Cap1 Rise

Active

Cap0 Fall

Active

Cap0 Rise

Active

----bbbb 00000000

2C TCAPINTS Reserved Cap1 Fall

Active

Cap1 Rise

Active

Cap0 Fall

Active

Cap0 Rise

Active

----bbbb 00000000

30 CPUCLKCR Reserved CPU

CLK Select

-------b 00000000

31 TMRCLKCR TCAPCLK Divider TCAPCLK Select ITMRCLK Divider ITMRCLK Select bbbbbbbb 10001111

32 CLKIOCR Reserved

XOSC

Select

XOSC

Enable

EFTB

Disabled

CLKOUT Select ---bbbbb 00000000

[+] Feedback [+] Feedback