CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 27 of 68

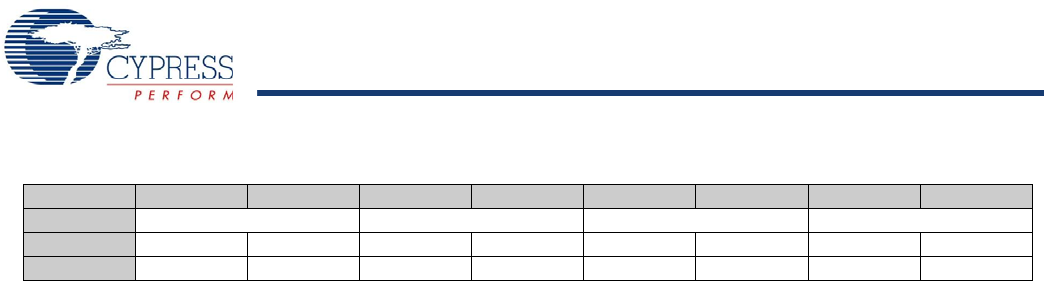

Table 12-5. Timer Clock Configuration (TMRCLKCR) [0x31] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field TCAPCLK Divider TCAPCLK Select ITMRCLK Divider ITMRCLK Select

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 1 0 0 0 1 1 1 1

Bit [7:6]: TCAPCLK Divider [1:0]

TCAPCLK Divider controls the TCAPCLK divisor.

0 0 = Divider Value 2

0 1 = Divider Value 4

1 0 = Divider Value 6

1 1 = Divider Value 8

Bit [5:4]: TCAPCLK Select

The TCAPCLK Select field controls the source of the TCAPCLK.

0 0 = Internal 24 MHz Oscillator

0 1 = External Crystal Oscillator—external crystal oscillator on CLKIN and CLKOUT if the external crystal oscillator is enabled,

CLKIN input if the external crystal oscillator is disabled (the XOSC Enable bit of the CLKIOCR Register is cleared—Table 12-4.)

1 0 = Internal 32 kHz Oscillator

1 1 = TCAPCLK Disabled

Note The 1024 μs interval timer is based on the assumption that TCAPCLK is running at 4 MHz. Changes in TCAPCLK frequency

cause a corresponding change in the 1024 μs interval timer frequency.

Bit [3:2]: ITMRCLK Divider

ITMRCLK Divider controls the ITMRCLK divisor.

0 0 = Divider value of 1

0 1 = Divider value of 2

1 0 = Divider value of 3

1 1 = Divider value of 4

Bit [1:0]: ITMRCLK Select

0 0 = Internal 24 MHz Oscillator

0 1 = External crystal oscillator—external crystal oscillator on CLKIN and CLKOUT if the external crystal oscillator is enabled,

CLKIN input if the external crystal oscillator is disabled.

1 0 = Internal 32 kHz Oscillator

1 1 = TCAPCLK

Note Changing the source of TMRCLK requires both the source and destination clocks to be running. It is not possible to change

the clock source away from TCAPCLK after that clock is stopped.

[+] Feedback [+] Feedback