54 DS8000 Series: Concepts and Architecture

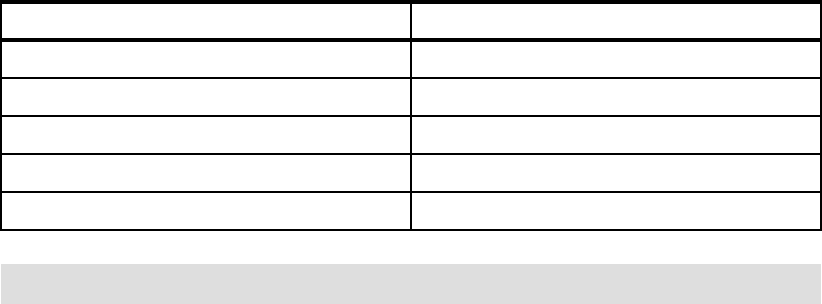

Table 3-1 Model conversions regarding LPAR functionality

3.3 LPAR security through POWER™ Hypervisor (PHYP)

The DS8300 Model 9A2 provides two storage facility images. This offers a number of

desirable business advantages. But it also can raise some concerns about security and

protection of the storage facility images in the DS8000 series. In this section we explain how

the DS8300 delivers robust isolation between the two storage facility images.

One aspect of LPAR protection and security is that the DS8300 has a dedicated allocation of

the hardware resources for the two facility images. There is a clear split of processors,

memory, I/O slots, and disk enclosures between the two images.

Another important security feature which is implemented in the pSeries server is called the

POWER Hypervisor (PHYP). It enforces partition integrity by providing a security layer

between logical partitions. The POWER Hypervisor is a component of system firmware that

will always be installed and activated, regardless of the system configuration. It operates as a

hidden partition, with no processor resources assigned to it.

Figure 3-6 on page 55 illustrates a set of address mapping mechanisms which are described

in the following paragraphs.

In a partitioned environment, the POWER Hypervisor is loaded into the first Physical Memory

Block (PMB) at the physical address zero and reserves the PMB. From then on, it is not

possible for an LPAR to access directly the physical memory. Every memory access is

controlled by the POWER Hypervisor.

Each partition has its own exclusive page table, which is also controlled by the POWER

Hypervisor. Processors use these tables to transparently convert a program's virtual address

into the physical address where that page has been mapped into physical memory.

In a partitioned environment, the operating system uses hypervisor services to manage the

translation control entry (TCE) tables. The operating system communicates the desired I/O

bus address to logical mapping, and the hypervisor translates that into the I/O bus address to

physical mapping within the specific TCE table. The hypervisor needs a dedicated memory

region for the TCE tables to translate the I/O address to the partition memory address, then

the hypervisor can perform direct memory access (DMA) transfers to the PCI adapters.

From Model To Model

921 (2-way processors without LPAR) 9A2 (4-way processors with LPAR)

922 (4-way processors without LPAR) 9A2 (4-way processors with LPAR)

9A2 (4-way processors with LPAR) 922 (4-way processors without LPAR)

92E (expansion frame without LPAR) 9AE (expansion frame with LPAR)

9AE (expansion frame with LPAR) 92E (expansion frame without LPAR)

Note: Every model conversion is a disruptive operation.