10 Design Guide

Intel

®

31244 PCI-X to Serial ATA Controller

About This Document

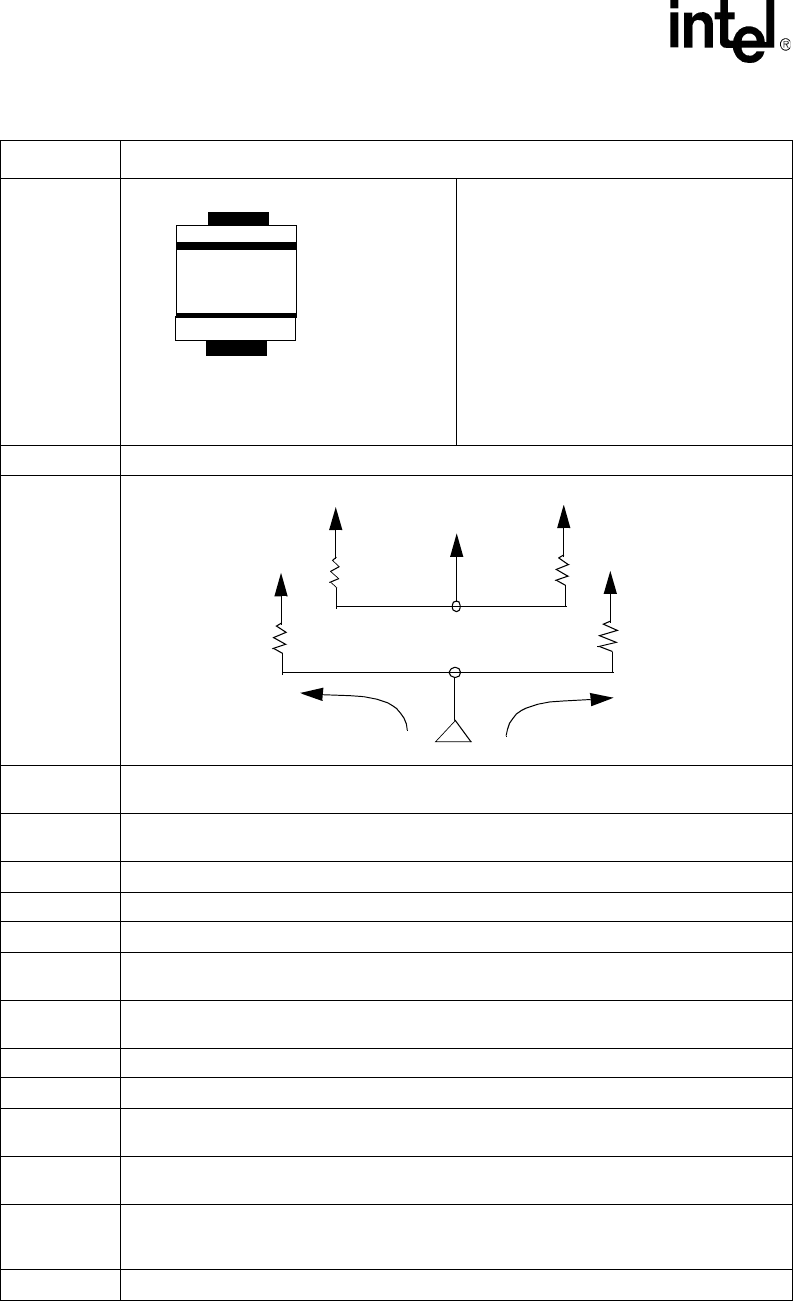

PCB

Printed circuit board.

Example manufacturing process consists of

the following steps:

• Consists of alternating layers of core and

prepreg stacked

• The finished PCB is heated and cured.

• The via holes are drilled

• Plating covers holes and outer surfaces

• Etching removes unwanted copper

• Board is tinned, coated with solder mask

and silk screened

JEDEC Provides standards for the semiconductor industry.

Aggressor

A network that transmits a coupled signal to another network is aggressor network.

Victim

A network that receives a coupled cross-talk signal from another network is a called the victim

network

Network

The trace of a PCB that completes an electrical connection between two or more

components.

Stub Branch from a trunk terminating at the pad of an agent.

CRB Customer Reference Board

HBA Host Bus Adapter

TX + / TX -

These signals are the outbound high-speed differential signals that are connected to the

serial ATA cable.

RX + / RX -

These signals are the inbound high-speed differential signals that are connected to the serial

ATA cable.

TX This is a transmit port that contains the basic high-speed driver electronics.

RX This is a receiver port contains the basic high-speed receiver electronics.

Termination

calibration

This block is used to establish the impedance of the RX block in order to properly terminate

the high-speed serial cable.

PLL

This block is used to synchronize an internal clocking reference so that the input high-speed

data stream may be properly decoded.

Voltage

Regulator

This block stabilizes the internal voltages used in the other blocks so that reliable operation

may be achieved. This block may or may not be required for proper operation of the balance

of the circuitry. The need for this block is implementation specific.

TxData Serially encoded 10b data attached to the high-speed serial differential line driver.

Table 2. Terminology and Definition (Sheet 2 of 3)

Term Definition

Layer 1: copper

Prepreg

Layer 2: GND

Core

Layer 3: VCC

Layer 4: copper

Prepreg

Example of a Four-Layer Stack

Aggressor Network

Victim Network

Zo

Zo

Zo

Zo