Design Guide 49

Intel

®

31244 PCI-X to Serial ATA Controller

PCI-X Layout Guidelines

7.3 PCI General Layout Guidelines

For acceptable signal integrity with bus speeds up to 133 MHz it is important to PCB design layout

have controlled impedance.

• Signal traces have an unloaded impedance of 60 +/- 10% Ω.

• Signal trace velocity is roughly 150 – 190 ps/inch

The below list provides general guidelines used when routing your PCI bus signals:

• Avoid routing signals > 8”.

• All clock nets must be on the top layer.

• All 32-bit interface signals from the PCI edge fingers must be no longer than 1.5” and no

shorter than 0.75”.

• All 64-bit extension signal from the PCI edge fingers must be no longer than 2.75” and no

shorter than 1.75”.

• CLK from the PCI edge finger must be 2.5” +/- 0.1”.

• P_RST# from the PCI edge finger must be no longer than 3.0” and no shorter than 0.75”.

• The following signals have no length restrictions: INTA#, INTB#, INTC#, INTD#, TCK,

TDI, TDO, TMS and TRST#

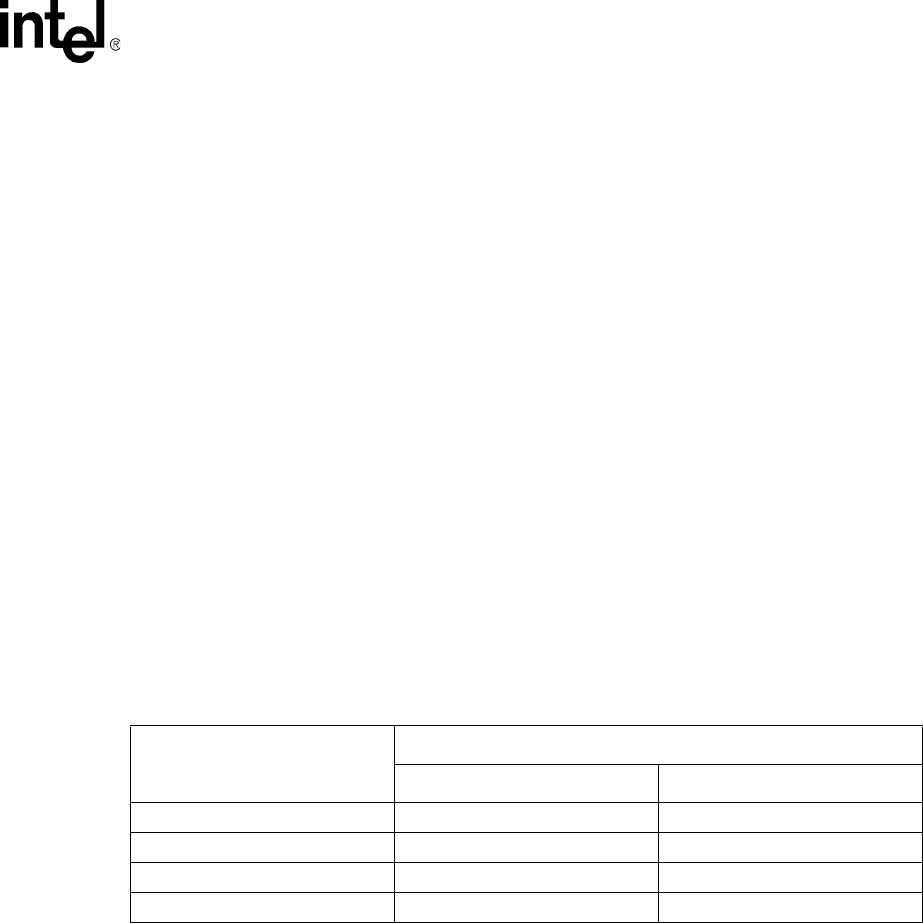

Table 20 provides information on maximum lengths for routing add-on card signals.

Do not use more than one via for the primary PCI bus signals.

Table 20. Add-on Card Routing Parameters

Parameter

PCI-X

Minimum Maximum

CLK 2.4 2.6

P_AD[0 – 31] 0.75 1.5

P_AD[32 – 63] 1.75 2.75

P_RST# 0.75 3.0