18 Design Guide

Intel

®

31244 PCI-X to Serial ATA Controller

Intel

®

31244 PCI-X to Serial ATA Controller Package

3.1 Signal Pin Descriptions

The signal pin descriptions for the GD31244 are provided as a reference. A complete list is also

available in the Intel

®

31244 PCI-X to Serial ATA Controller Datasheet.

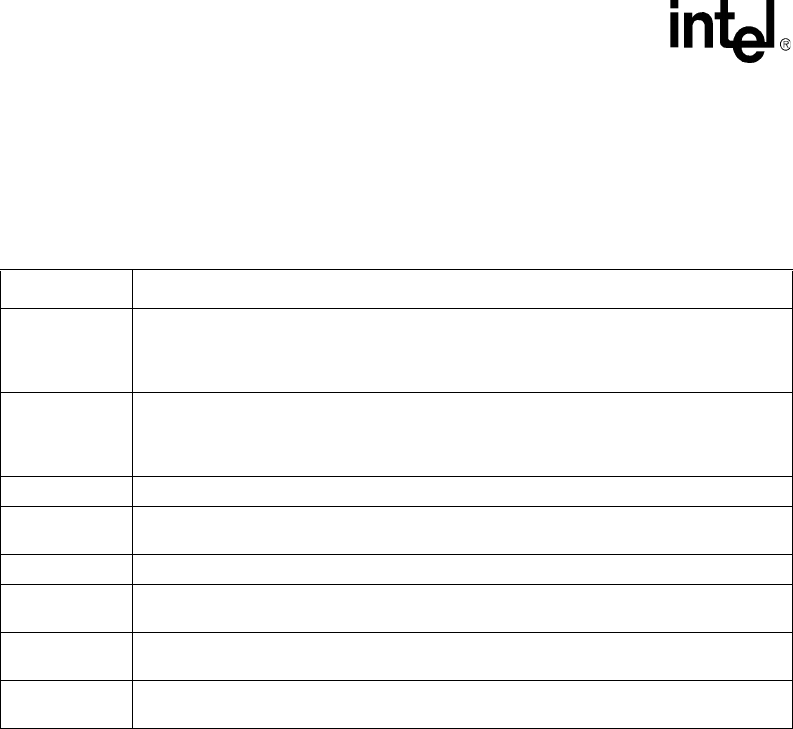

Table 3. Serial ATA Signals Pin Descriptions

Name Description

TX0P, TX0N,

TX1P, TX1N,

TX2P, TX2N,

TX3P, TX3N

OUTPUT - Differential High-Speed Outputs: These are the differential serial outputs for

each channel. When disabled, these outputs are driven to their DC-Bias point.

RX0P, RX0N,

RX1P, RX1N,

RX2P, RX2N,

RX3P, RX3N

INPUT - Differential High-Speed Inputs: These are the differential serial inputs for each

channel.

CLKOUT OUTPUT - LVTTL: This is connected to one side of the 37.5 MHz crystal.

CLKIN

INPUT - LVTTL: This is the reference clock input for the clock multiplier unit at 37.5 MHz. It

may be connected to either an external clock source or one side of a crystal.

CLKO Buffered output of the 37.5 MHz clock.

RBIAS

INPUT - ANALOG: This pin is pull-down to ground with a 1000 Ω, 1% resistor in order to set

the internal termination resistors to 1000 Ω.

CAP0, CAP1

Analog: An external 0.1 µF (+/- 10%) capacitor is connected between these pins to set the

Clock Multiplier PLL loop filter response.

LED0, LED1,

LED2

†

, LED3

†

OUTPUT - LVTTL: These are the Activity LED outputs for channel 0, channel1, channel 2

and channel 3 (active LOW with 10 mA maximum sink capability).

† LED2 and LED3 are dual purpose pins. Refer to Table 7.