48 Design Guide

Intel

®

31244 PCI-X to Serial ATA Controller

PCI-X Layout Guidelines

7.2 PCI/X Clocking Modes

The Intel

®

31244 PCI-X to serial ATA controller clocking modes for PCI-X and PCI bus are shown

in Table 19. At PCI bus reset, the Intel

®

80321 I/O processor samples the P_FRAME#,

P_IRDY#, P_TRDY#, P_STOP#, and P_DEVSEL# to determine the operating frequency for

PCI-X mode. When P_FRAME# is deasserted and P_IRDY# is deasserted (i.e., the bus is idle)

and one or more of P_DEVSEL#, P_STOP#, and P_TRDY# are asserted at the rising edge of

P_RST#, the device enters PCI-X mode (see Table 19). Otherwise, the device enters conventional

PCI mode. With conventional PCI mode, a low on M66EN determines the PCI bus is at 66 MHz.

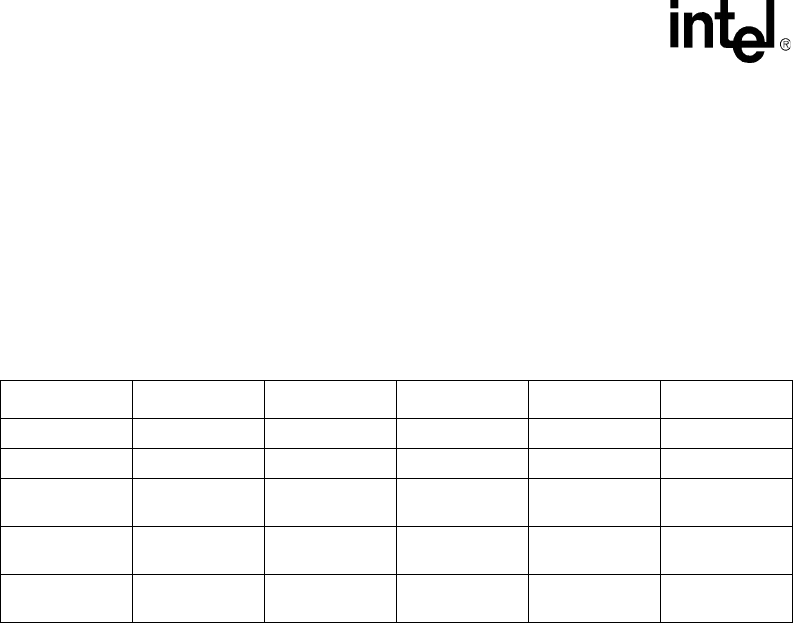

Table 19. PCI-X Clocking Modes

Mode/CLK PCI/XCAP M66EN P_DEVSEL# P_STOP# P_TRDY#

PCI 33 MHz GND Deasserted Deasserted Deasserted Deasserted

PCI 66 MHz GND Asserted Deasserted Deasserted Deasserted

PCI-X 66 MHz

10 KΩ 0.01 µF

cap to GND

N/A Deasserted Deasserted Asserted

PCI-X 100 MHz

0.01 µF cap to

GND

N/A Deasserted Asserted Deasserted

PCI-X 133 MHz

0.01 µF cap to

GND

N/A Deasserted Asserted Asserted