52 Design Guide

Intel

®

31244 PCI-X to Serial ATA Controller

PCI-X Layout Guidelines

7.4.3 Connecting Intel

®

31244 PCI-X to Serial ATA Controller

to Single-Slot

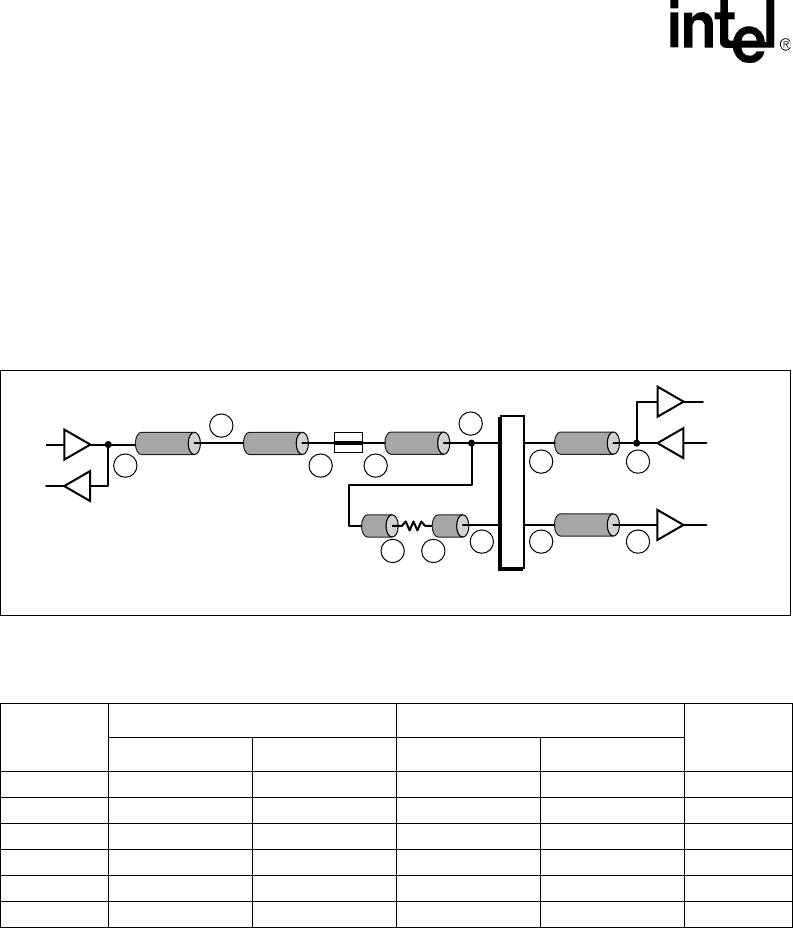

Figure 17 shows one of the chipset PCI AD lines connected through W1 and W12 line segments, to

a single-slot connector through W13 line segment, to the GD31244. This AD line is also used as an

IDSEL line from line segment W14 to a 2K resistor through W15 to the PCI connector. The other

end of the PCI connector IDSEL line connects through W16 to GD31244 IDSEL line input buffer.

Table 22 shows the wiring lengths for a single slot design. This design layout wiring lengths should

support PCI-X speeds. However, prelayout simulation is recommended.

.

• Stublengths are represented by W#s

Note: W14, W15 and W16 represent the IDSEL line. W14 and W15 <= 0.8”.

Figure 17. Single-Slot Topology

A9126-01

W1 W11 W12

W14 W15

2K

W16

W13

Host

Slot 1

PCI Connector

1413

191817

1615

12

2

1 10 11

Table 22. Wiring Lengths for Single Slot

Segment

Lower AD Bus Upper AD Bus

Units

Minimum Length Maximum Length Minimum Length Maximum Length

W1 2.0 8 2 7 inches

W12 0.1 0.5 0.1 0.5 inches

W13 0.75 1.5 1.75 2.75 inches

W14 0.1 Note N/A N/A inches

W15 Note 0.6 N/A N/A inches

W16 1.125 1.125 N/A N/A inches