Design Guide 7

Intel

®

31244 PCI-X to Serial ATA Controller

Contents

Revision History

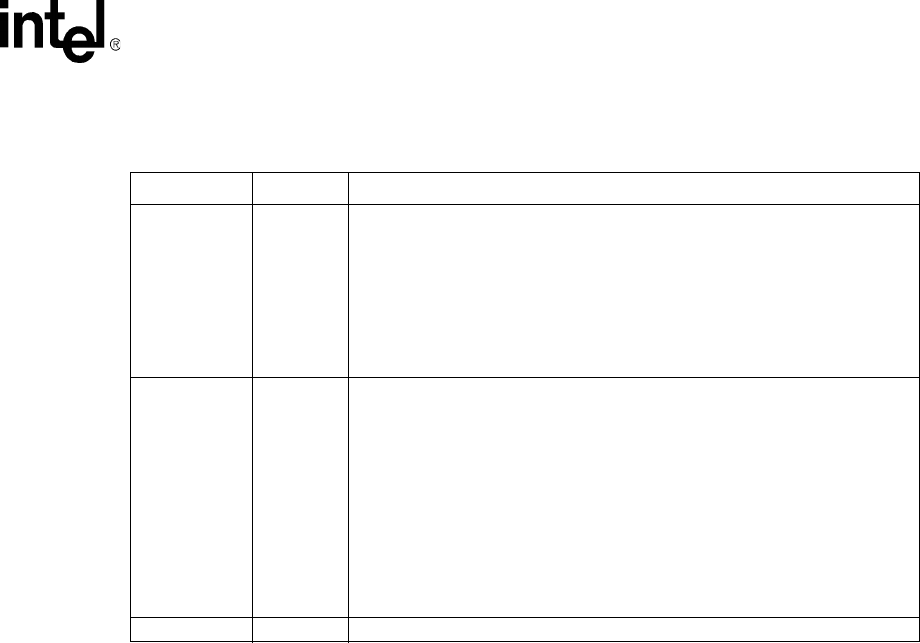

Date Revision # Description

April 2004 003 Removed Section 5.4.5, “Spread Spectrum Clocking” on page 35.

Removed SSC pin in Table 2, “Terminology and Definition” on page 9.

Updated SSCEN pin in Table 5, “Configuration Pin Descriptions” on page 20 and

Table 30, “Terminations: Pull-up/Pull-down” on page 65.

Removed Section 9.1, “Power Delivery for the Intel® 31244 PCI-X to Serial ATA

Controller (TBD)” on page 59.

In Appendix A, “Intel

®

IQ31244 Controller Evaluation Platform Board Bill of

Materials”, replaced Bill of Materials table with a URL to the Intel

®

website.

December 2002 002 In Section 2.1, added a new table titled “Serial ROM Interface Pin Descriptions”.

In Section 2.1, added note to Table 2, “Serial ATA Signal Pin Descriptions”,

indicating that LED2 and LED3 as dual purpose pins.

Replaced Figure 5, “PBGA Mapped by Pin Function” with a revised illustration.

Added content to Section 3.4.1.1, “Intel GD31244 PCI-X to Serial ATA Controller

Decoupling”, regarding the use of at least twelve 0.1 µF capacitors to decouple

the VCC 2.5 V signal.

Removed Section 3.4.1.2, “PCI-X Decoupling”.

In Table 30, “Terminations: Pullup/Pulldown”, revised row with signal name of

TRST# to include TDI#, TMS#, and TCK as 4.7K pull-ups.

In Appendix A, revised the Bill of Materials.

October 2002 001 Initial release of this document.