5-18 Lucent Technologies Inc.

USS-720

Instant USB

Preliminary Data Sheet, Rev. 5

USB-to-

IEEE

1284 Bridge September 1999

13

IEEE

1284 Port (continued)

EPP Address Register

EPP Data Register

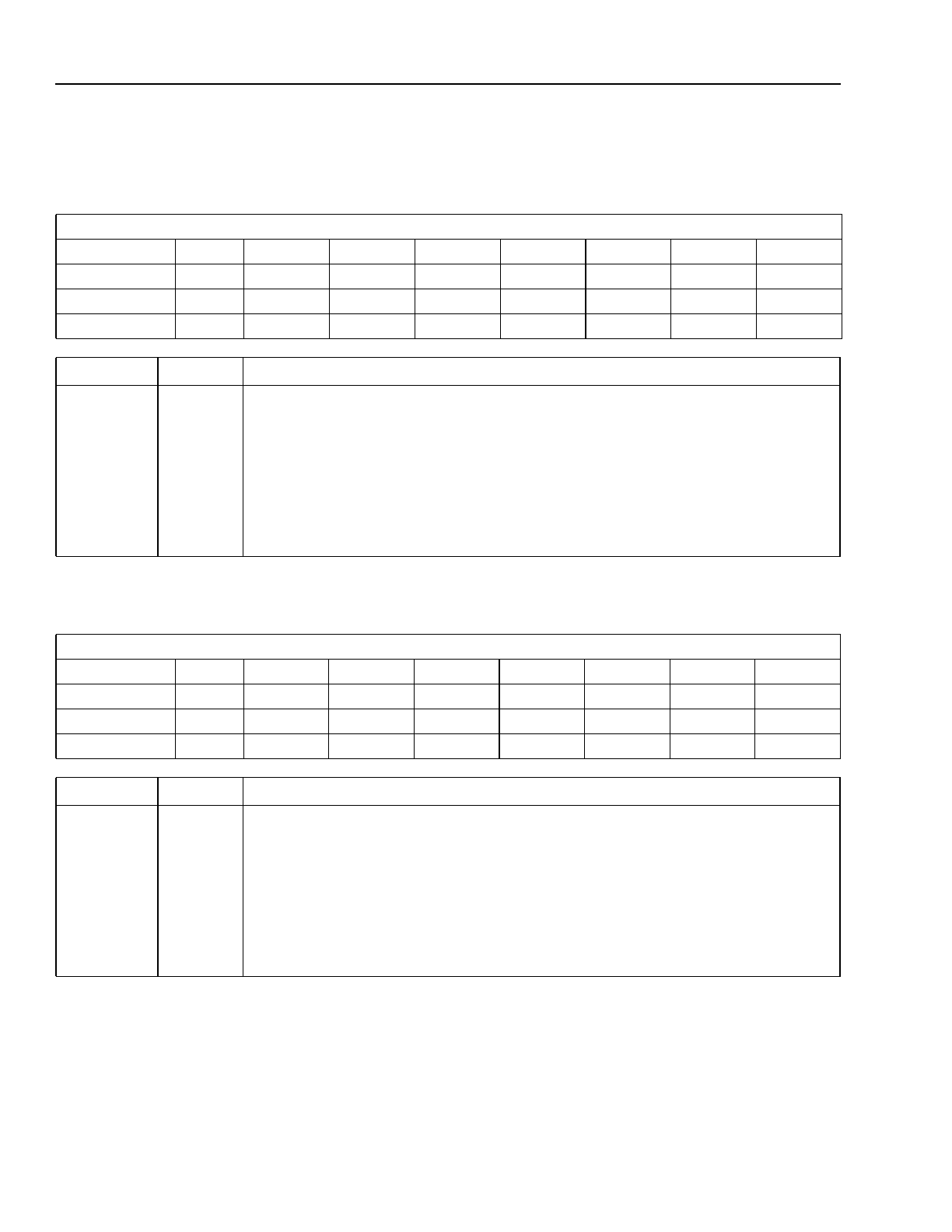

Table 24. EPP Address Register

EPP Address Register Address: 3

Bit 7 6 5 4 3 2 1 0

Symbol A7 A6 A5 A4 A3 A2 A1 A0

Access R/W R/W R/W R/W R/W R/W R/W R/W

Default X X X X X X X X

Bit Symbol Bit Description

7—0 A7—A0 EPP Address. This register is equivalent to and operates in the same manner as the

EPP Address Register in a standard host-side parallel port controller chip. The

register is writable when Auto Mode is 0 and the Mode field in the Extended Control

Register is set to 100. A write to this register initiates an EPP address write transfer

on the parallel port. The register is always readable. When the Mode is set to 100, a

read access will initiate an EPP address read transfer on the parallel port, and the

value returned will be the address value read from the peripheral. Reads when not in

Mode 100 will return whatever value has been previously latched, but will not have

any effect on the parallel port.

Table 25. EPP Data Register

EPP Data Register Address: 4

Bit 7 6 5 4 3 2 1 0

Symbol D7 D6 D5 D4 D3 D2 D1 D0

Access R/W R/W R/W R/W R/W R/W R/W R/W

Default X X X X X X X X

Bit Symbol Bit Description

7—0 D7—D0 EPP Data. This register is equivalent to and operates in the same manner as the EPP

Data Register in a standard host-side parallel port controller chip. The register is writ-

able when Auto Mode is 0 and the Mode field in the Extended Control Register is set

to 100. A write to this register initiates an EPP data write transfer on the parallel port.

The register is always readable. When the Mode is set to 100, a read access will

initiate an EPP data read transfer on the parallel port, and the value returned will be

the data value read from the peripheral. Reads, when not in Mode 100, will return

whatever value has been previously latched, but will not have any effect on the

parallel port.