Preliminary Data Sheet, Rev. 5 USS-720

Instant USB

September 1999 USB-to-

IEEE

1284 Bridge

Lucent Technologies Inc. 5-21

13

IEEE

1284 Port (continued)

USS-720 Control Register

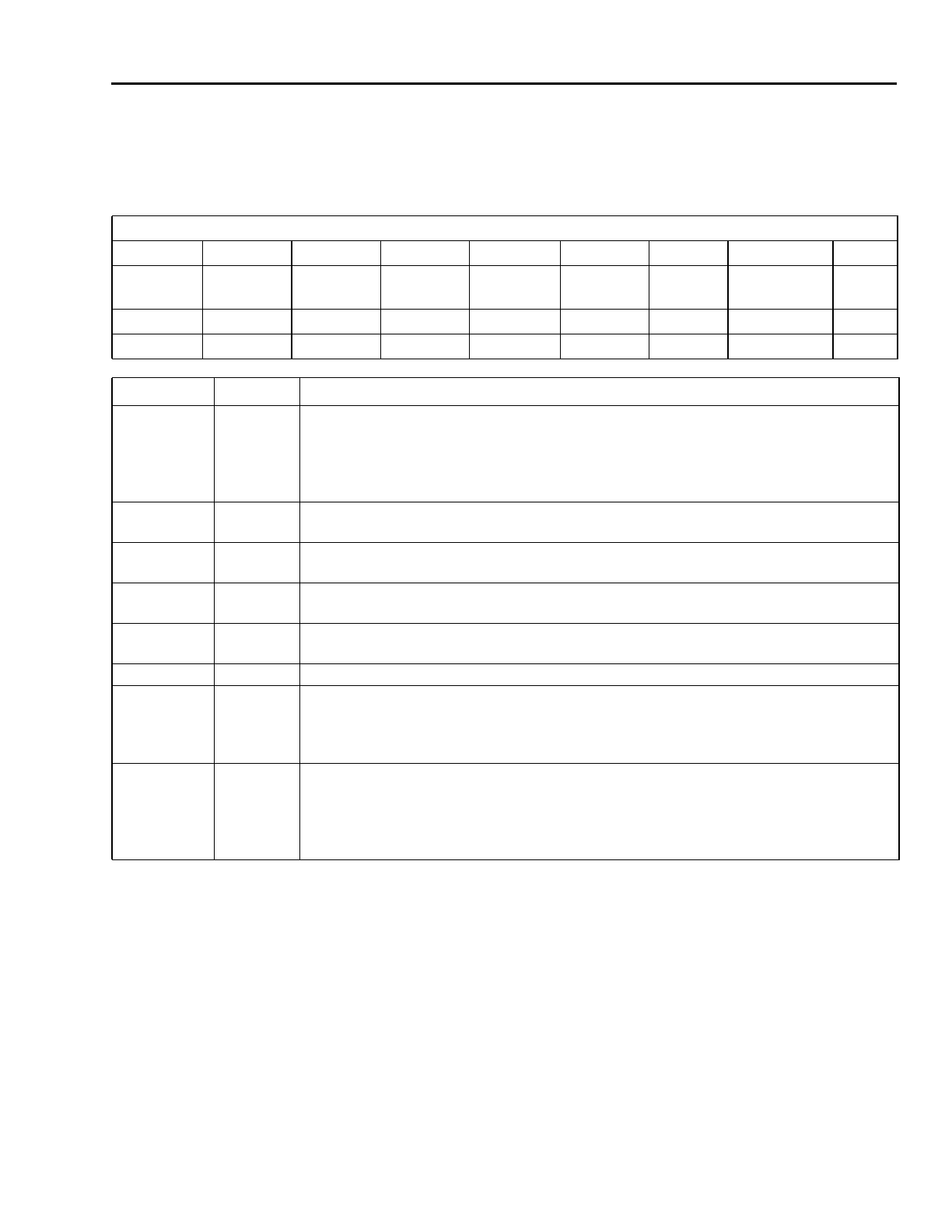

Table 28. USS-720 Control Register

USS-720 Control Register Address: 7

Bit 7 6 5 4 3 2 1 0

Symbol Discon.

int mask

Change

int mask

Bulk In

int mask

Bulk Out

int mask

nFault

int mask

Reserved Compress

enable

Auto

mode

Access R/W R/W R/W R/W R/W R/W R/W R/W

Default 1 1 1 1 1 0 1 1

Bit Symbol Bit Description

7 Discon.int

mask

Disconnect Interrupt Mask. This bit masks the generation of an interrupt on the

detection of what appears to be a disconnection of the peripheral from the parallel

port. Disconnect is detected when the Peripheral Logic High signal changes from 1 to

0, or when all parallel port lines driven by the peripheral are high for a long period of

time.

6 Change

int mask

Change Interrupt Mask. This bit masks the generation of an interrupt on the detec-

tion of a transition on any of the parallel port lines driven by the peripheral.

5 Bulk In int

mask

Bulk In Interrupt Mask. This bit masks the generation of an interrupt when Bulk In

data is available for reading by the host.

4 Bulk Out

int mask

Bulk Out Interrupt Mask. This bit masks the generation of an interrupt when the Bulk

Out data path goes empty.

3 nFault int

mask

nFault Interrupt Mask. This bit masks the generation of an interrupt falling edge of

nFault when Mode is set to 011 (ECP Mode).

2 Reserved Reserved. This bit must always be written to 0.

1 Compress

enable

Compress Enable. This bit enables automatic hardware-based RLE compression of

outgoing data, for use in ECP with RLE Mode. If software desires to use this feature,

this bit should be set before attempting to send data. This bit must be cleared for

proper operation in ECP (without RLE) Mode.

0 Auto

mode

Auto Mode. Setting this bit puts the chip in fully Automatic Mode. When set, USS-720

can handle all communications with the peripheral with no assistance from software,

and all registers except the USS-720 Control Register are read only. Clearing this bit

enables write access to the other registers and disables all automatic operation,

provided that none has yet taken place.