11 - 70 11 - 70

MELSEC-Q

11 TROUBLESHOOTING

Special Register List (Continued)

Number Name Meaning Explanation

Set by

(When set)

Corresponding

ACPU

D9

Corresponding

CPU

SD64 D9125

SD65 D9126

SD66 D9127

SD67 D9128

SD68 D9129

SD69 D9130

SD70 D9131

SD71 D9132

SD72 New

SD73 New

SD74 New

SD75 New

SD76 New

SD77 New

SD78 New

SD79

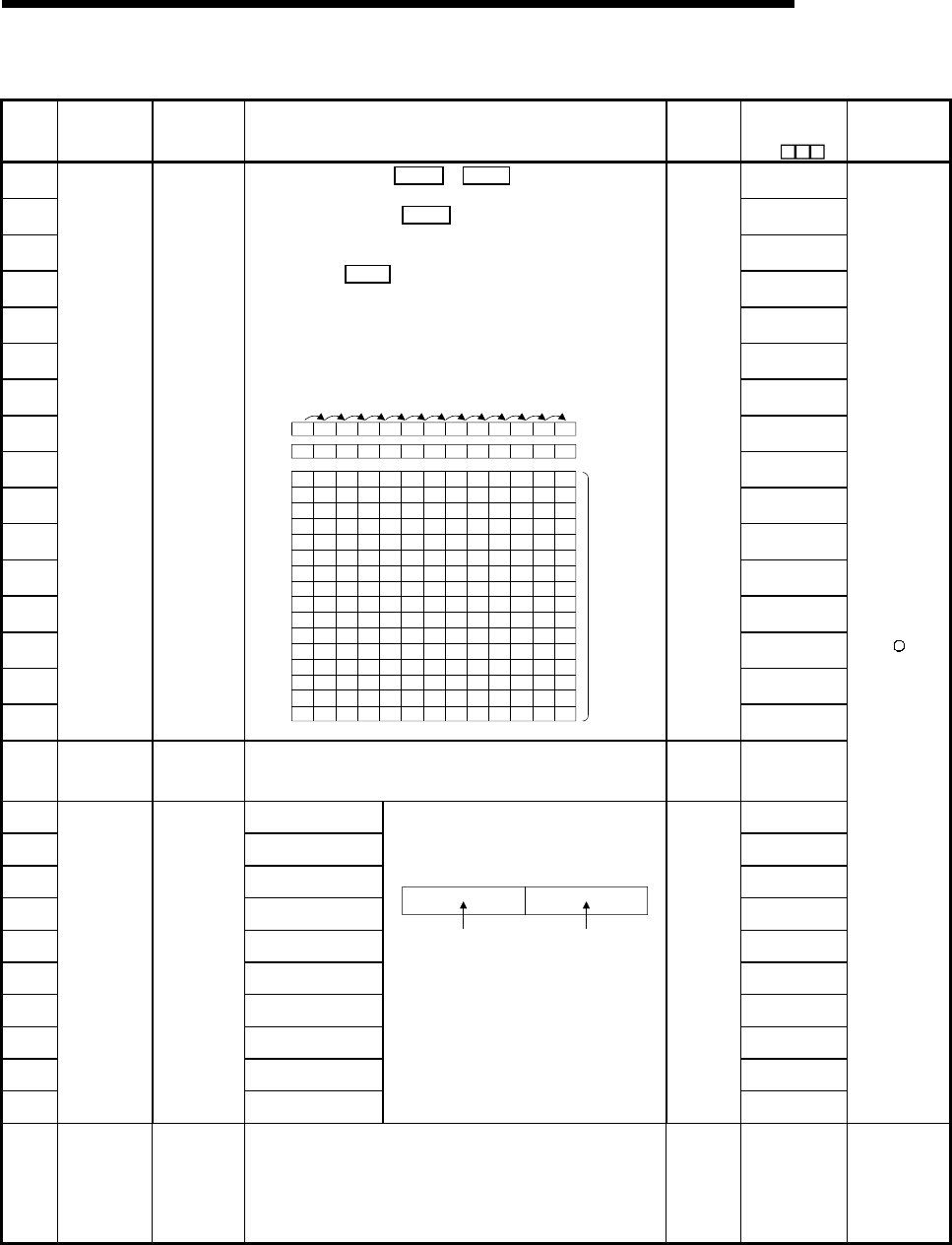

Table of

detected

annunciator

numbers

Annunciator

detection

number

When F goes ON due to OUT F or SET F , the F numbers which

go progressively ON from SD64 through SD79 are registered.

F numbers turned OFF by RST F are deleted from SD64 to SD79,

and are shifted to the data register following the data register where

the deleted F numbers had been stored.

Execution of the LEDR instruction shifts the contents of SD64 to

SD79 up by one.

(This can also be done by using the INDICATOR RESET switch on

the of the Q3A/Q4ACPU.)

After 16 annunciators have been detected, detection of the 17th will

not be stored from SD64 through SD79.

SD62 0

50 50 50 50 50 50 50 50 50 50 50 99

...(Number

detected)

SD630123234567898

0 505050505050505050505099SD64

SD65

SD66

SD67

SD68

SD69

SD70

SD71

SD72

SD73

SD74

SD75

SD76

SD77

SD78

SD79

0 0 25 25 99 99 99 99 99 99 99 99 15

0 0 0 99 0 15 15 15 15 15 15 15 70

0 0 0 0 0 0 70 70 70 70 70 70 65

0 0 0 0 0 0 0 656565656538

0 0 0 0 0 0 0 0 38 38 38 38 110

000000000110110110151

00151

0

00000000 151

210

000000000 0 0210

0000000000 0 00

0000000000 0 00

0000000000 0 00

0000000000 0 00

0000000000 0 00

0000000000 0 00

0000000000 0 00

...(Number of

annunciators

detected)

(Number

detected)

SET

F50

SET

F25

SET

F99

RST

F25

SET

F15

SET

F70

SET

F65

SET

F38

SET

F110

SET

F151

SET

F210LEDR

S

(Instruction

execution)

New

SD80 CHK number CHK number

• Error codes detected by the CHK instruction are stored as BCD

code.

S

(Instruction

execution)

New

SD90 Corresponds to SM90 D9108

SD91 Corresponds to SM91 D9109

SD92 Corresponds to SM92 D9110

SD93 Corresponds to SM93 D9111

SD94 Corresponds to SM94 D9112

SD95 Corresponds to SM95 D9113

SD96 Corresponds to SM96 D9114

SD97 Corresponds to SM97 New

SD98 Corresponds to SM98 New

SD99

Step transition

watchdog

timer setting

value

(Enabled only

when SFC

program

exists)

F number for

timer set value

and time over

error

Corresponds to SM99

• F numbers which go ON at step transition

watchdog timer set value and watchdog timer

over errors.

B15 B7 B0B8

F number setting

(0 to 255)

Timer time limit

setting

(1 to 255 s:

(1-s units))

• Timer is started by turning SM90 through

SM99 ON during active step, and if the

transition conditions for the relevant steps are

not met within the timer limits, the designated

annunciator (F) will go ON.

U

New

SD105

CH1

transmission

speed setting

(RS-232)

Stores the

preset

transmission

speed when

GX Developer

is used.

3 : 300bps, 6 : 600bps, 24 : 2400bps, 48 : 4800bps

96 : 9600bps, 192 : 19.2kbps, 384 : 38.4kbps

576 : 57.6kbps, 1152 : 115.2kbps

S New

QCPU

Remote