2 Instructions

2-76

CP1E CPU Unit Instructions Reference Manual(W483)

• When a TTIM(087)/TTIMX(555) timer is forced set, its Completion Flag will be turned ON and its PV

will be reset to 0. When a TTIM(087)/TTIMX(555) timer is forced reset, its Completion Flag will be

turned OFF and its PV will be reset to 0. The forced set and forced reset operations take priority over

the status of the timer and reset inputs.

• The timer’s PV is refreshed only when TTIM(087)/TTIMX(555) is executed, so the timer will not oper-

ate properly when the cycle time exceeds 100 ms because the timer increments in 100-ms units.

• The timer’s Completion Flag is refreshed only when TTIM(087)/TTIMX(555) is executed, so a delay of

up to one cycle may be required for the Completion Flag to be turned ON after the timer times out.

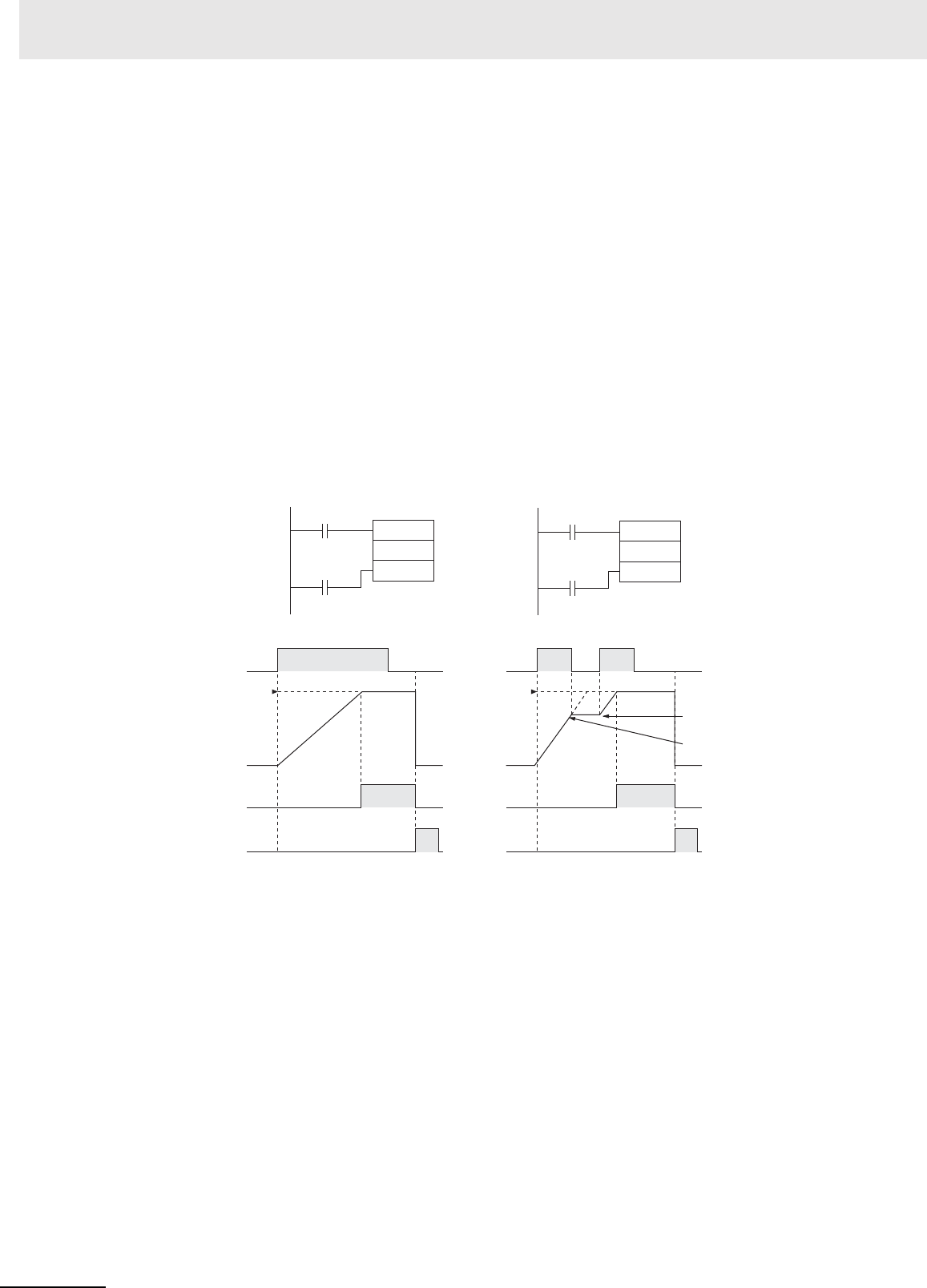

Sample program

When timer input CIO 0.00 is ON in the following example, the timer PV will begin counting up from 0.

Timer Completion Flag T0001 will be turned ON when the PV reaches the SV.

If the reset input is turned ON, the timer PV will be reset to 0 and the Completion Flag (T0001) will be

turned OFF. (Usually the reset input is turned ON to reset the timer and then the timer input is turned

ON to start timing.)

If the timer input is turned OFF before the SV is reached, the timer will stop timing but the PV will be

maintained. The timer will resume from its previous PV when the timer input is turned ON again.

0.00

T0001

T0001

Timer input

Timer PV

Timer Completion

Flag

Reset input

PV maintained.

Timing resumes.

or

ON

OFF

0

ON

OFF

ON

OFF

#0100

ON

OFF

0

ON

OFF

ON

OFF

#0100

0.01

TTIM

0001

#0100

0.00

TTIMX

0001

&0100

0.00

0.01