2-45

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Sequence Control Instructions

2

MILH/MILR/MILC

Function

When the execution condition for MILH(517) (or MILR(518)) with interlock number N is OFF, the outputs

for all instructions between that MILH(517)/MILR(518) instruction and the next MILC(519) with interlock

number N are interlocked.

When the execution condition for MILH(517) (or MILR(518)) with interlock number N is ON, the instruc-

tions between that MILH(517)/MILR(518) instruction and the next MILC(519) with interlock number N

are executed normally.

Interlock Status

The following table shows the treatment of various outputs in an interlocked section between

MILH(517)/MILR(518) instruction and the next MILC(519).

Note Bits and words in all other instructions including TTIM(087), TTIMX(555), SET, RSET, CNT, CNTX(546),

CNTR(012), CNTRX(548), SFT, and KEEP(011) retain their previous status.

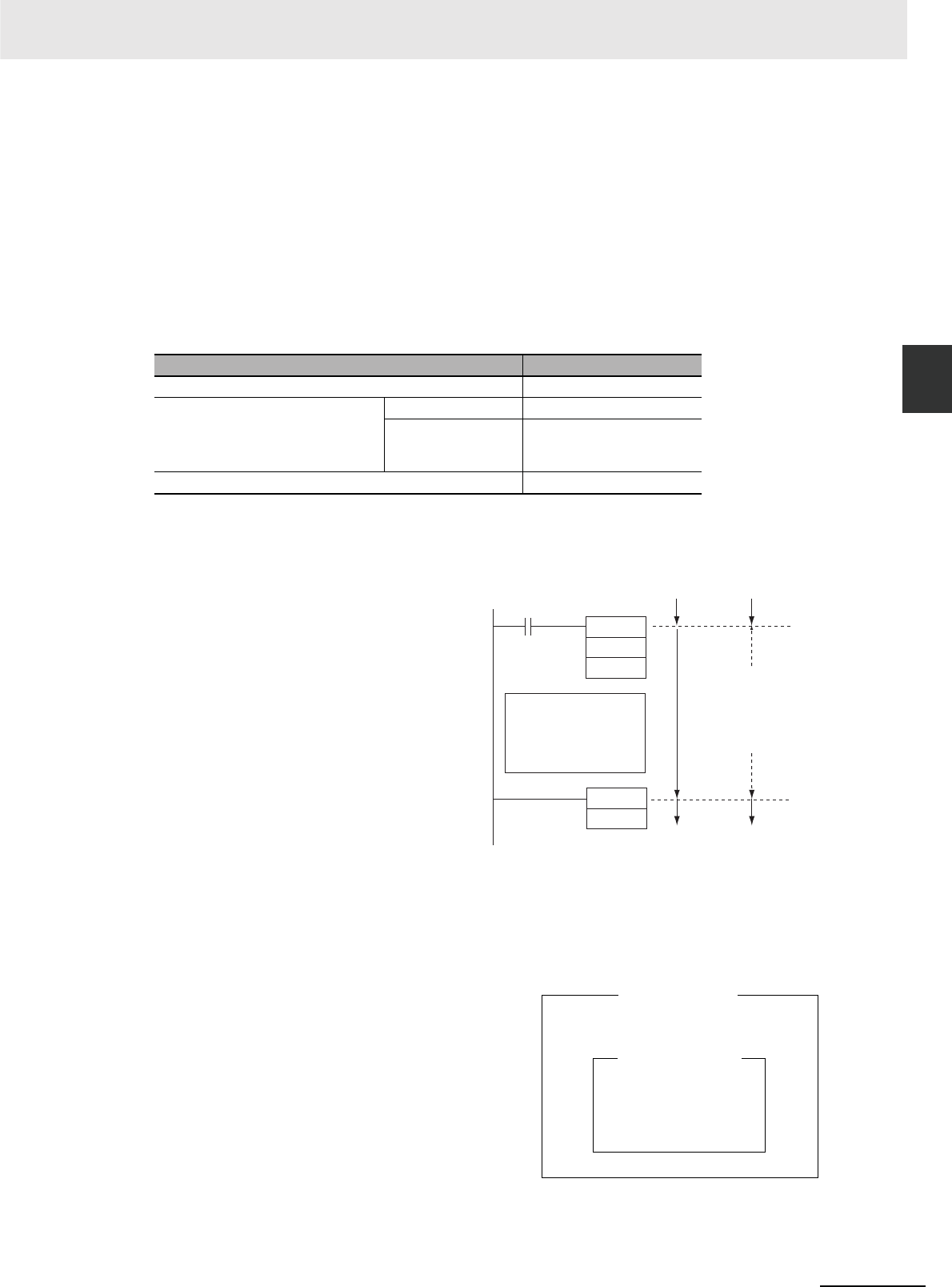

Nesting

Interlocks are nested when an interlocked program section (MILH(517)/MILR(518) and MILC(519) com-

bination) is placed within another interlocked program section (MILH(517)/MILR(518) and MILC(519)

combination). Interlocks can be nested up to 16 levels.

Nesting can be used for the following kinds of applications.

Instruction Treatment

Bits specified in OUT, OUT NOT OFF

TIM, TIMX(550), TIMH(015),

TIMHX(551), TMHH(540),

TMHHX(552), TIML(542), and

TIMXL(553)

Completion Flag OFF (reset)

PV Time set value (reset)

Bits/words specified in all other instructions (See note.) Retain previous status.

The MILH(517)/MILR(518) instruction turns

OFF the Interlock Status Bit (operand D)

when the interlock is in engaged and turns ON

the bit when the interlock is not engaged.

Consequently, the Interlock Status Bit can be

monitored to check whether or not the inter-

lock for a given interlock number is engaged.

Example 1

Interlocking the entire program with one con-

dition and interlocking a part of the program

with another condition (1 nesting level)

MILH

n

d

MILC

n

Input condition

Interlocked program

section

Input condition ON

(Normal operation)

Input condition OFF

Normal

operation

Interlock

Status Bit

(d) ON

Outputs interlocked.

(Outputs OFF, timers

reset, etc.)

Interlock Status Bit (d)

OFF

Global interlock

(Emergency stop)

A1 (Peripheral processing)

Partial interlock

(Conveyor RUN)

A2 (Conveyor operation)