2-77

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Timer and Counter Instructions

2

TIML/TIMLX

TIML/TIMLX

Applicable Program Areas

Operands

Operand Specifications

Flags

Instruction Mnemonic Variations

Function

code

Function

LONG TIMER

TIML --- 542

TIML(542)/TIMLX(553) operates a decrementing

timer with units of 0.1s.

TIMLX --- 553

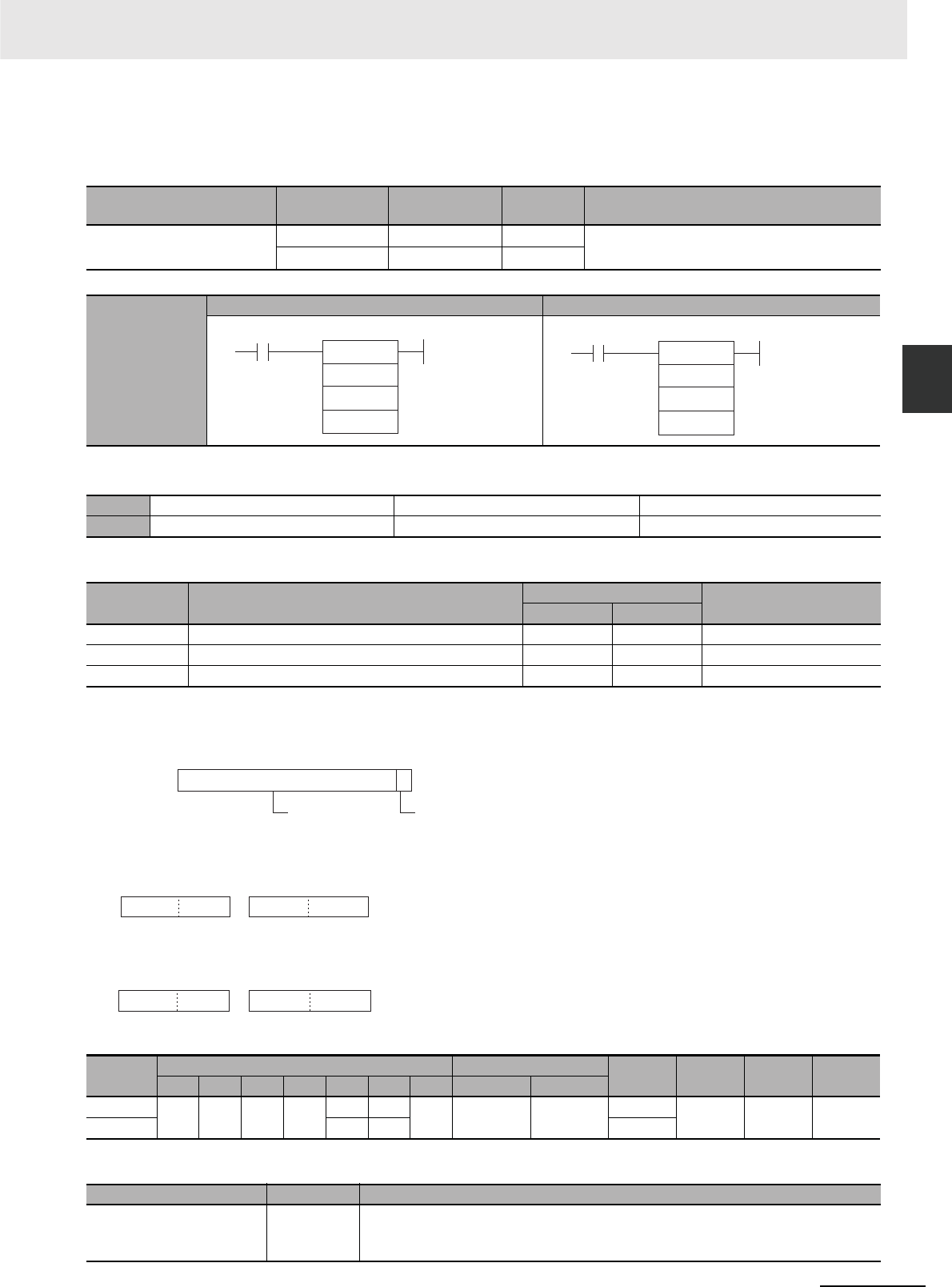

Symbol

TIML TIMLX

BCD Binary

Area Step program areas Subroutines Interrupt tasks

Usage OK OK Not allowed

Operand Description

Data type

Size

TIML TIMLX

D1 Completion Flag WORD UINT 1

D2 PV word DWORD UDINT 2

S SV word DWORD UDINT 2

D1: Completion Flag

D2: PV Word

S: SV Word

The PV and SV can range from #00000000

to #99999999 for TIML(542) and &00000000

to &4294967294 (decimal) or #00000000 to

#FFFFFFFF (hexadecimal) for TIMLX(553).

Note S, S+1, D2 and D2+1 must be in the same

data area.

Area

Word addresses Indirect DM addresses

Constants CF Pulse bits TR bits

CIO WR HR AR T C DM @DM *DM

D1,D2

OK OK OK OK

--- ---

OK OK OK

---

--- --- ---

SOKOK OK

Name Label Operation

Error Flag P_ER • ON if in BCD mode and D2 does not contained BCD data.

• ON if in BCD mode and S does not contained BCD data.

• OFF in all other cases.

TIML(542)

D1

D2

S

D1: Completion Flag

D2: PV word

S: SV word

TIMLX(553)

D1

D2

S

D1: Completion Flag

D2: PV word

S: SV word

15

D1

0

Completion Flag

Do not use.

D2D2+1

D2

D2+1 is the leftmost 4 digits,

D2 is the rightmost 4 digits

SS+1

S

S+1 is the leftmost 4 digits,

S is the rightmost 4 digits