Rev.1.10 Jul 01, 2005 page 118 of 318

REJ09B0124-0110

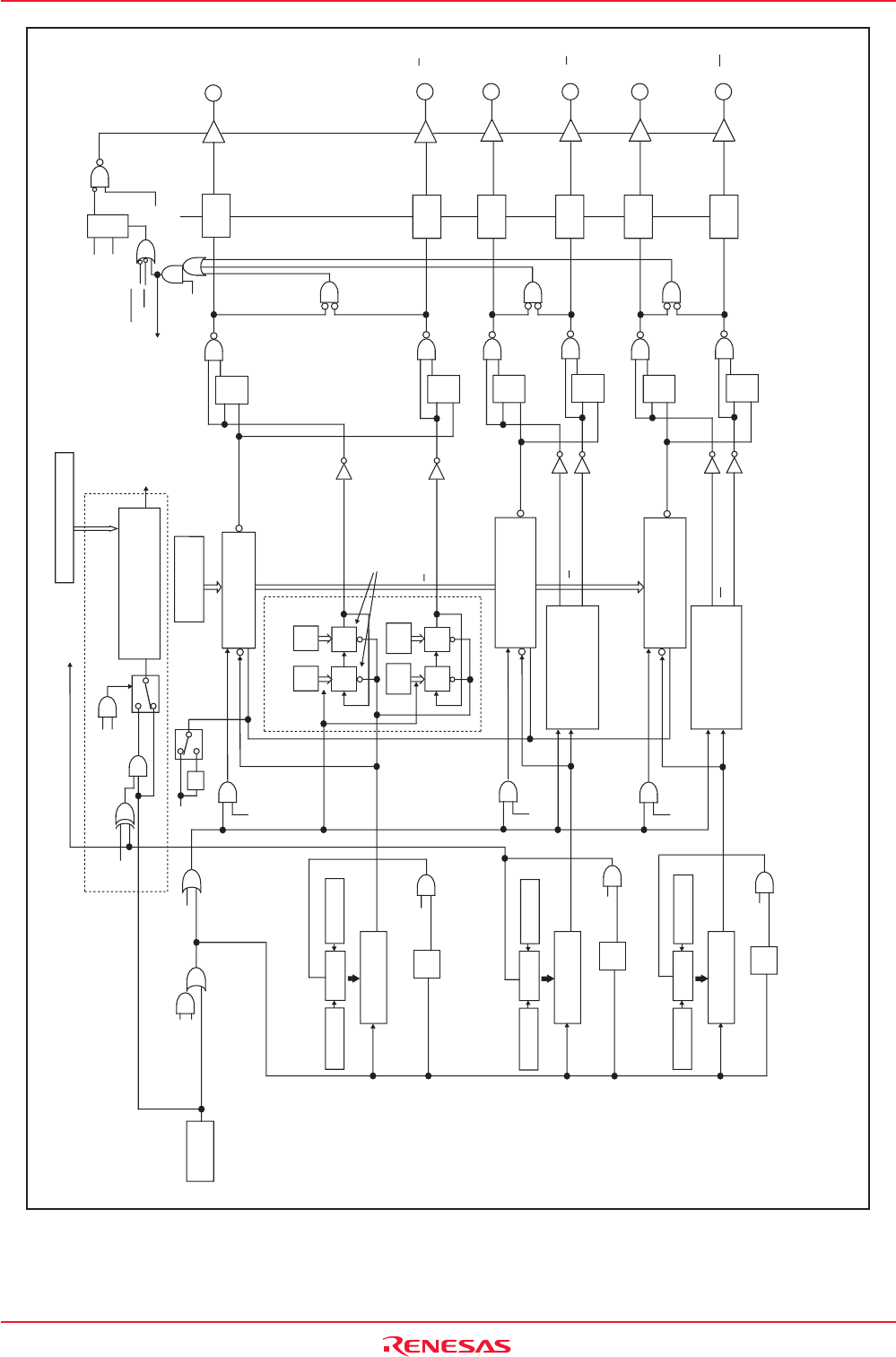

M16C/6N Group (M16C/6NK, M16C/6NM) 13. Three-Phase Motor Control Timer Function

Under development

This document is under development and its contents are subject to change.

Figure 13.1 Three-Phase Motor Control Timer Function Block Diagram

DUB1

bit

Timer B2

(Timer Mode)

Timer B2 Underflow

ICTB2 Counter

Interrupt Request Bit

U

U

V

V

W

W

NMI

RESET

R

D

D

T

Q

D

T

Q

D

T

Q

D

T

Q

D

T

Q

D

T

Q

Q

INV03

INV05

INV04

Timer A4 Counter

(One-Shot Timer Mode)

(One-Shot Timer Mode)

(One-Shot Timer Mode)

Trigger

TA4 Register

Reload

TA41 Register

Timer A1 Counter

Trigger

TA1 Register

Reload

TA11 Register

Timer A2 Counter

Trigger

TA2 Register

Reload

TA21 Register

INV07

T

Q

INV11

Dead Time Timer

INV00

1

0

INV01

INV11

DU0

bit

DU1

bit

T

DQ

T

DQ

DUB0

bit

T

DQ

T

DQ

U-phase Output

Control Circuit

U-Phase Output Signal

U-Phase Output Signal

V-Phase Output

Control Circuit

When setting the TA4S bit to "0", signal is

set to "0"

T

Q

INV11

T

Q

INV11

W-Phase Output

Control Circuit

V-Phase Output Signal

W-Phase Output Signal

V-Phase Output Signal

W-Phase Output Signal

Write Signal

to Timer B2

Start Trigger Signal for

Timers A1, A2, A4

Transfer

Trigger

(1)

INV10

Circuit to set Interrupt

Generation Frequency

Three-Phase Output

Shift Register

(U Phase)

f1 or f2

0

1

1/2

n=1 to 15

Reload Register

Dead Time Timer

n = 1 to 255

Dead Time Timer

n = 1 to 255

n = 1 to 255

Trigger

INV06

Trigger

Trigger

Trigger

Trigger

Trigger

INV06

INV06

INV14

INV13

ICTB2 Register n=1 to 15

Timer B2

n = 1 to 255

INV12

Reload Control Signal for

Timer A4

When setting the TA1S bit to "0", signal is set

to "0"

When setting the TA2S bit to "0", signal is

set to "0"

Switching to P8_0, P8_1 and P7_2 to P7_5 is not shown in this diagram.

Inverse

Control

Inverse

Control

Inverse

Control

Inverse

Control

Inverse

Control

Inverse

Control

Timer A4

One-Shot

Pulse

Value to be written

to INV03 bit

Write signal to

INV03 bit

T

INV02

INV00 to INV07: Bits in INVC0 register

INV10 to INV15: Bits in INVC1 register

DUi, DUBi: Bits in IDBi register (i = 0, 1)

TA1S to TA4S: Bits in TABSR register

NOTE:

1.Transfer trigger is generated at only when the IDB0 and IDB1 registers are set and the first timer B2 underflows, if the INV0

6 bit is set to "0" (triangular wave modulation mode).