Rev.1.10 Jul 01, 2005 page 149 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

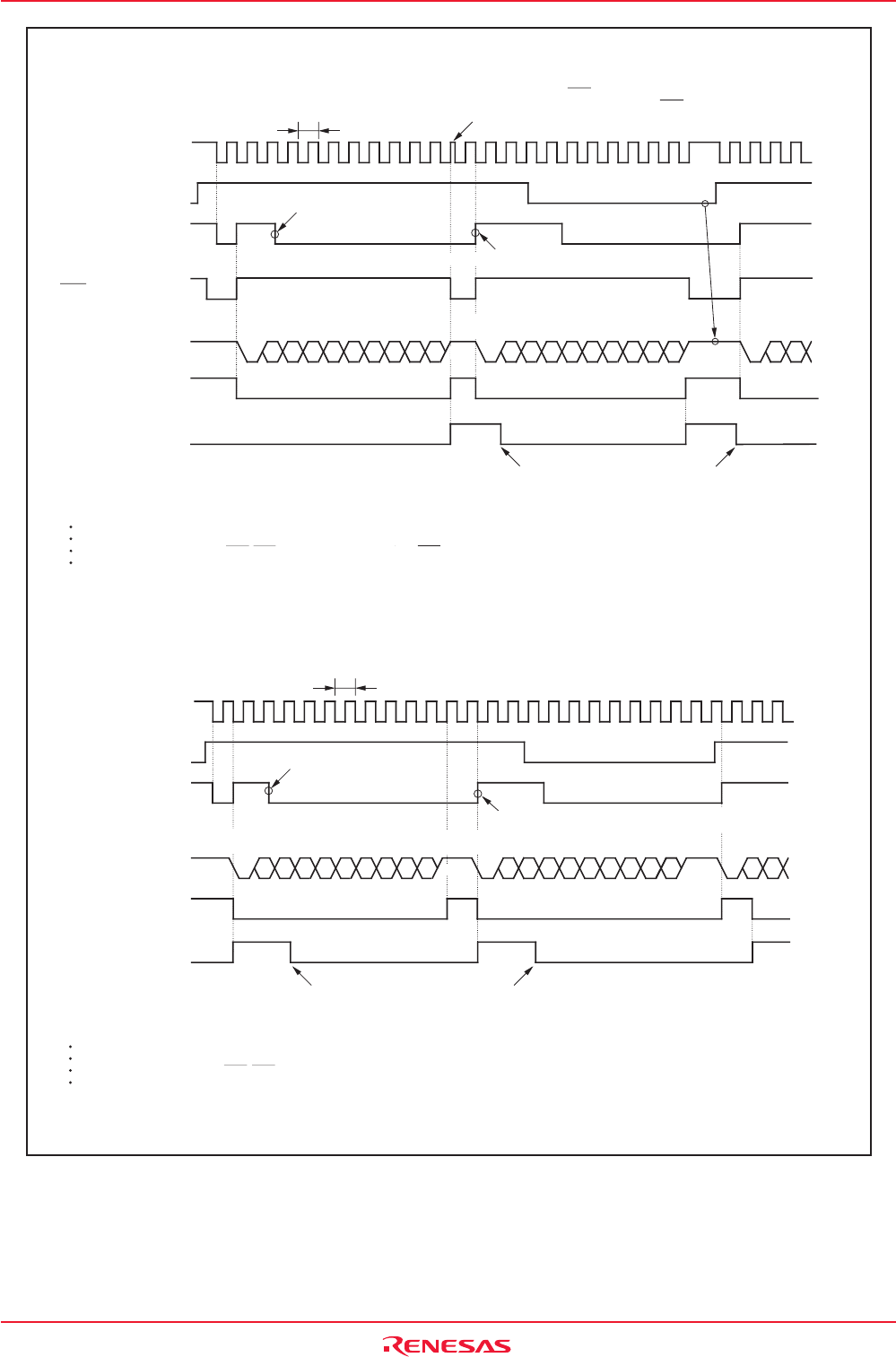

(1) Example of Transmit Timing when Transfer Data is 8-bit Long (parity enabled, one stop bit)

(2) Example of Transmit Timing when Transfer Data is 9-bit Long (parity disabled, two stop bits)

Figure 14.17 Transmit Operation

Start

bit

Parity

bit

TXDi

CTSi

"1"

"0"

"1"

"L"

"H"

"0"

"1"

TC = 16 (n + 1) / fj or 16 (n + 1) / fEXT

fj : frequency of UiBRG count source (f1SIO, f2SIO, f8SIO, f32SIO)

fEXT : frequency of UiBRG count source (external clock)

n : value set to UiBRG

i = 0 to 2

"0"

"1"

TXDi

"0"

"1"

"0"

"1"

"0"

"1"

Transfer clock

TC

"0"

"1"

TC

Transfer clock

D0

D1

D2

D3

D4

D5

D6

D7

ST

P

D0

D1

D2

D3

D4

D5

D6

D7

SP

ST

P

SP

D0

D1

ST

Stop

bit

Start

bit

The transfer clock stops momentarily as CTS

i is "H" when the stop bit is checked.

The transfer clock starts as the transfer starts immediately CTSi changes to "L".

D0

D1

D2

D3

D4

D5

D6

D7

ST

SP

D8

D0

D1

D2

D3

D4

D5

D6

D7

ST

D8

D0

D1

ST

SPSP

Stop

bit

Stop

bit

"0"

SP

Stopped pulsing

because the TE bit

= 0

Write data to the UiTB register

TE bit in

UiC1 register

TI bit in

UiC1 register

TXEPT bit in

UiC0 register

IR bit in

SiTIC register

Transferred from UiTB register to UARTi transmit register

The above timing diagram applies to the case where the register bits are set

as follows:

PRYE bit in UiMR register = 1 (parity enabled)

STPS bit in UiMR register = 0 (1 stop bit)

CRD bit in UiC0 register = 0 (CTS/RTS enabled), and CRS bit = 0 (CTS selected)

UilRS bit = 1 (an interrupt request occurs when transmit completed):

U0IRS bit is bit 0 in UCON register

U1IRS bit is bit 1 in UCON register

U2IRS bit is bit 4 in U2C1 register

Set to "0" by an interrupt request acknowledgement or by program

TE bit in

UiC1 register

TI bit in

UiC1 register

TXEPT bit in

UiC0 register

IR bit in

SiTIC register

Set to "0" by an interrupt request acknowledgement or by program

Write data to the UiTB register

Transferred from UiTB register to UARTi

transmit register

TC = 16 (n + 1) / fj or 16 (n + 1) / fEXT

fj : frequency of UiBRG count source (f1SIO, f2SIO, f8SIO, f32SIO)

fEXT: frequency of UiBRG count source (external clock)

n : value set to UiBRG

i = 0 to 2

The above timing diagram applies to the case where the register bits are set

as follows:

PRYE bit in UiMR register = 0 (parity disabled)

STPS bit in UiMR register = 1 (2 stop bits)

CRD bit in UiC0 register = 1 (CTS/RTS disabled)

UilRS bit = 0 (an interrupt request occurs when transmit buffer becomes empty):

U0IRS bit is bit 0 in UCON register

U1IRS bit is bit 1 in UCON register

U2IRS bit is bit 4 in U2C1 register