Rev.1.10 Jul 01, 2005 page 130 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

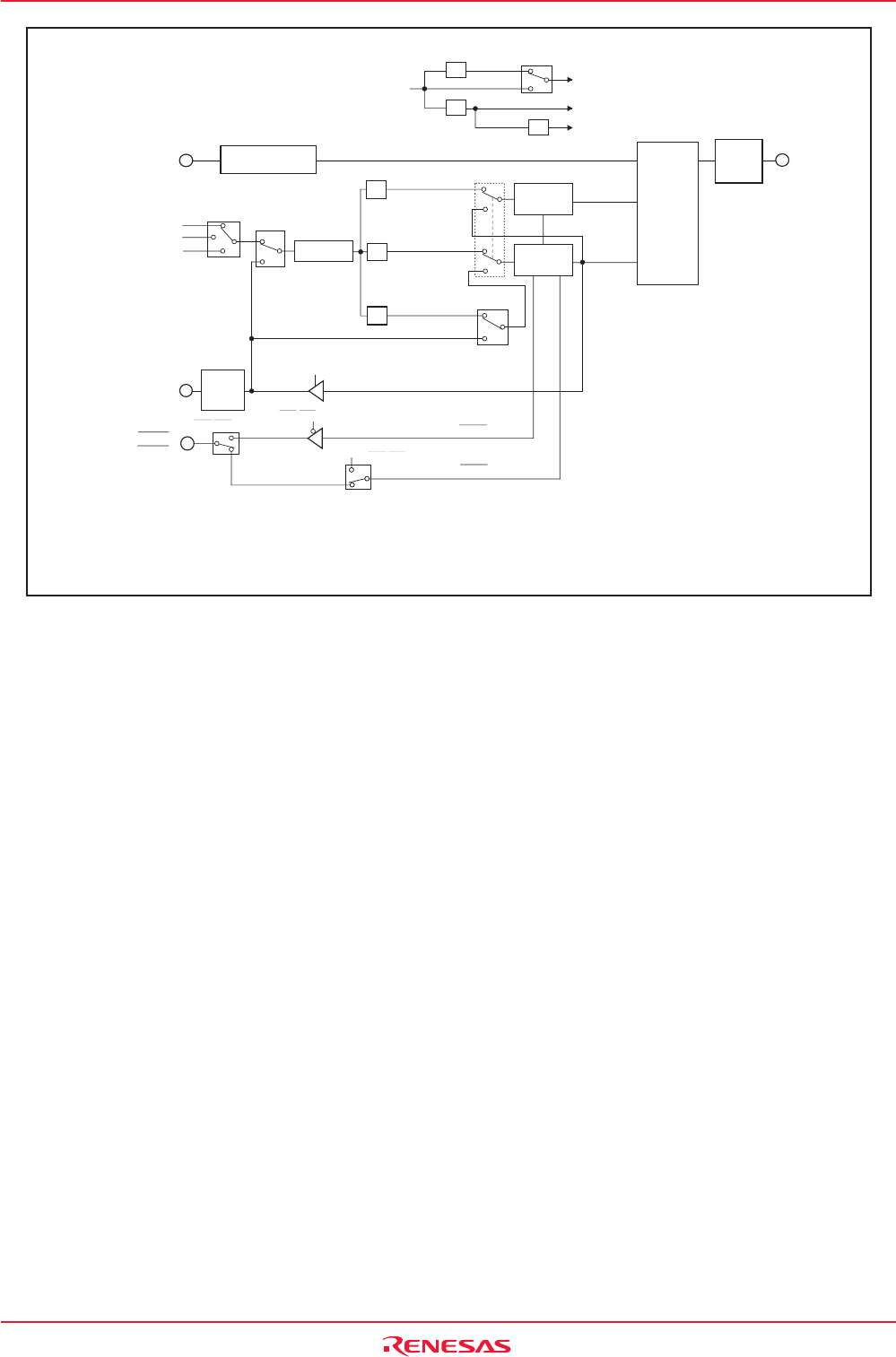

Figure 14.3 UART2 Block Diagram

RXD2

1 / (n2+1)

1/16

1/16

1/2

U2BRG

register

Clock synchronous type

(when internal clock is selected)

Clock synchronous

type

Clock synchronous type

(when internal clock is selected)

Clock synchronous type

(when external clock is selected)

CLK2

Clock source selection

f1SIO or f2SIO

f8SIO

f32SIO

Internal

External

RTS2

CTS2

TXD2

(UART2)

CLK

polarity

reversing

circuit

CLK1 to CLK0

00

01

10

CKDIR

CKPOL

UART reception

UART transmission

Clock synchronous

type

CKDIR

1

0

RXD polarity reversing

circuit

0

1

VSS

0

1

SMD2 to SMD0

010, 100, 101, 110

001

010, 100, 101, 110

001

0

1

CRS

CRD

CTS2 /

RTS2

n2: Values set to the U2BRG register

PCLK1: Bit in PCLKR register

SMD2 to SMD0, CKDIR: Bits in U2MR register

CLK1 to CLK0, CKPOL, CRD, CRS: Bits in U2C0 register

CTS/RTS disabled

CTS/RTS disabled

CTS/RTS selected

Reception

control circuit

Transmission

control circuit

Receive

clock

Transmit

clock

TXD

polarity

reversing

circuit

(1)

Transmit/

receive

unit

PCLK1

f1SIO or f2SIO

1/2

Main clock, PLL clock, or on-chip oscillator clock

1/2

1/8

f8SIO

f32SIO

f1SIO

f2SIO

0

1

1/4