Ladder Logic Elements and Instructions

384

870 USE 101 00 V.3

Standard Ladder Logic Elements, Continued

Standard Ladder

Logic

Instructions,

Continued

Continued on next page

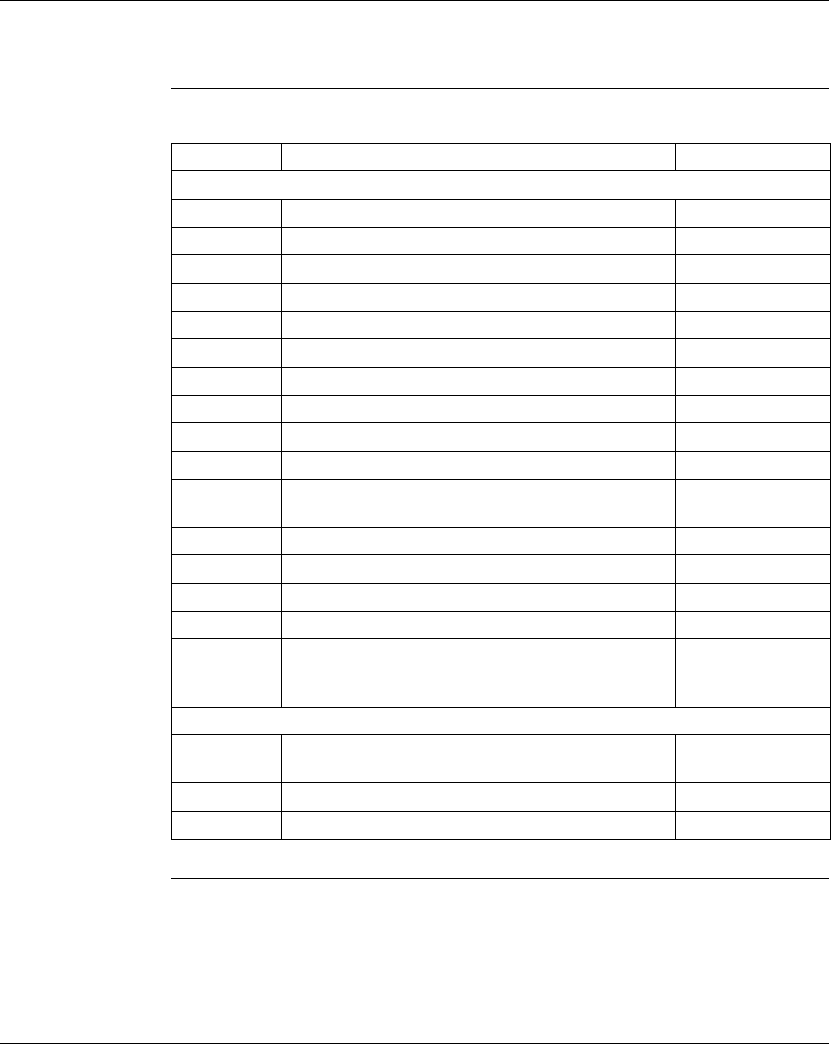

Symbol Meaning Nodes Consumed

DX Matrix Instructions

AND Logically ANDs two matrices 3

OR Does logical inclusive OR of two matrices 3

XOR Does logical exclusive OR of two matrices 3

COMP Performs logical complement of values in a matrix 3

CMPR Logically compares values in two matrices 3

MBIT Logical bit modify 3

SENS Logical bit sense 3

BROT Logical bit rotate 3

AD16 Signed/unsigned 16-bit addition 3

SU16 Signed/unsigned 16-bit subtraction 3

TEST Compares the magnitudes of the values in the top and

middle nodes

3

MU16 Signed/unsigned 16-bit multiplication 3

DV16 Signed/unsigned 16-bit division 3

ITOF Signed/unsigned integer-to-floating point conversion 3

FTOI Floating point-to-signed/unsigned integer conversion 3

EMTH Performs 38 math operations, including floating point

math operations and extra integer math operations

such as square root

3

Ladder Logic Subroutine Instructions

JSR Jumps from scheduled logic scan to a ladder logic

subroutine

2

LAB Labels the entry point of a ladder logic subroutine 1

RET Returns from the subroutine to scheduled logic 1