DDR2CLKOUT

DDR2CLKOUT

DSDCKE

DCE0

DSDWE

DSDRAS

DSDCAS

DSDDQM0

DSDDQM1

DSDDQS0

DSDDQS1

DBA[2:0]

DEA[13:0]

DED[15:0]

ODT0

DSDDQS0

DSDDQS1

CK

CK

CKE

CS

WE

RAS

CAS

LDM

LDQS

UDQS

BA[2:0]

A[12:0]

DQ[15:0]

ODT

V

REF

LDQS

UDQS

DDR2

Memory

x16-bit

DDR2

Memory

Controller

ODT1

DSDDQGATE0

(A)

DSDDQGATE1

(A)

DSDDQGATE2

(A)

DSDDQGATE3

(A)

DDRSLRATE

DED[31:16]

DSDDQM2

DSDDQM3

DSDDQS2

DSDDQS3

DSDDQS2

DSDDQS3

UDM

CK

CK

CKE

CS

WE

RAS

CAS

LDM

LDQS

UDQS

BA[2:0]

A[12:0]

DQ[15:0]

ODT

LDQS

UDQS

DDR2

Memory

x16-bit

UDM

V

REF

V

DD

V

REF

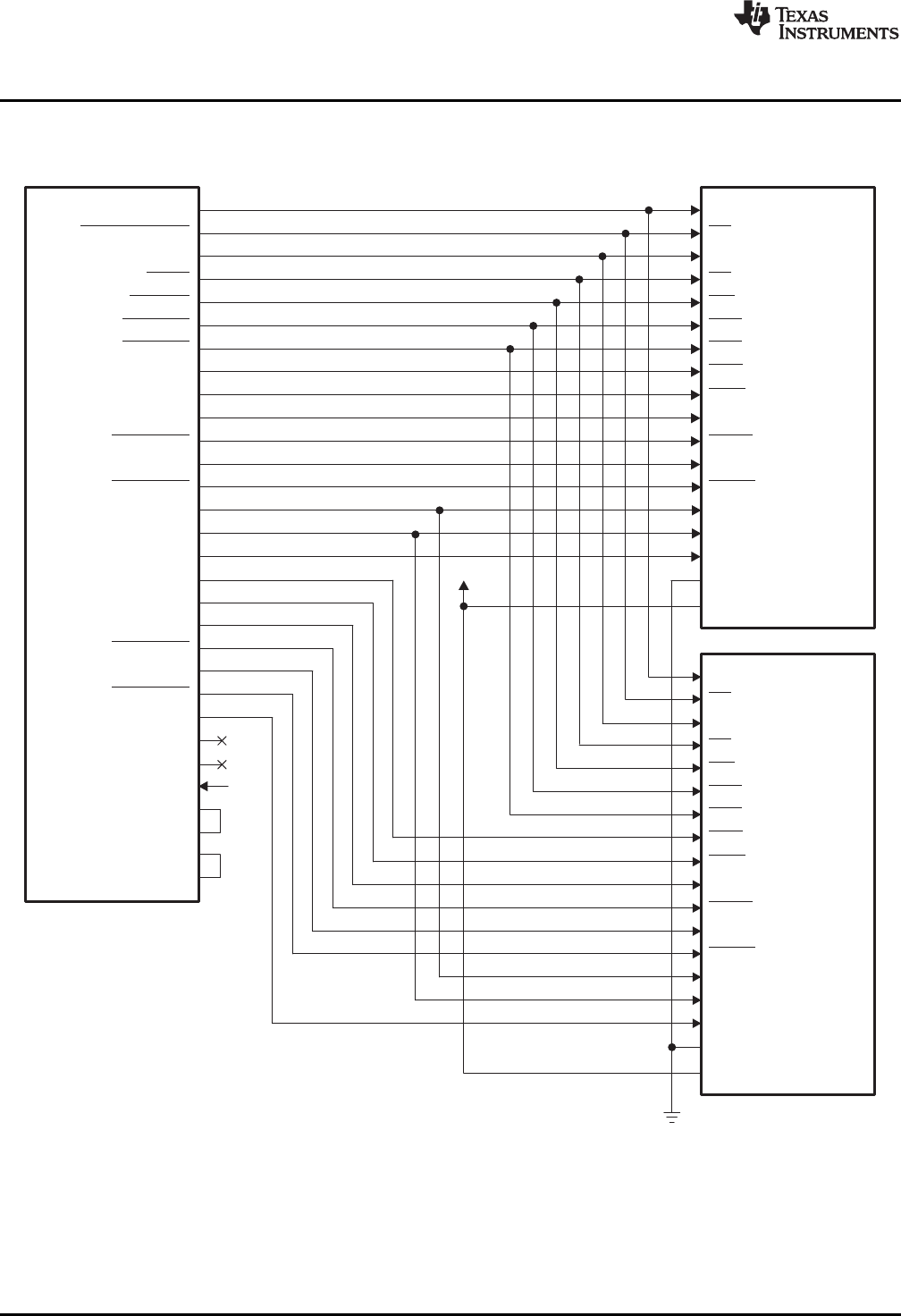

Using the DDR2 Memory Controller

www.ti.com

Figure 16. Connecting to Two 16-Bit DDR2 SDRAM Devices

A These pins are used as a timing reference during memory reads. For routing rules, see the device-specific data

manual.

32

C6455/C6454 DDR2 Memory Controller SPRU970G–December 2005–Revised June 2011

Submit Documentation Feedback

Copyright © 2005–2011, Texas Instruments Incorporated