www.ti.com

PeripheralArchitecture

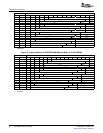

SDCFGBitLogicalAddress

IBANKPAGESIZE31:28272625242322:17161514131211109:2

00XXXXXnrb=14

(1)

ncb=8

10XXXXnrb=14nbb=1ncb=8

20XXXnrb=14nbb=2ncb=8

30XXnrb=14nbb=3ncb=8

01XXXXnrb=14ncb=9

11XXXnrb=14nbb=1ncb=9

21XXnrb=14nbb=2ncb=9

31Xnrb=14nbb=3ncb=9

02XXXnrb=14ncb=10

12XXnrb=14nbb=1ncb=10

22Xnrb=14nbb=2ncb=10

32Xnrb=13nbb=3ncb=10

03XXnrb=14ncb=11

13Xnrb=14nbb=1ncb=11

23Xnrb=12nbb=2ncb=11

33Xnrb=11nbb=3ncb=11

(1)

Legend:nrb=numberofrowaddressbits;ncb=numberofcolumnaddressbits;nbb=numberofbankaddressbits;BE=byte

enablebits.

Figure12.LogicalAddress-to-DDR2SDRAMAddressMapfor16-bitSDRAM

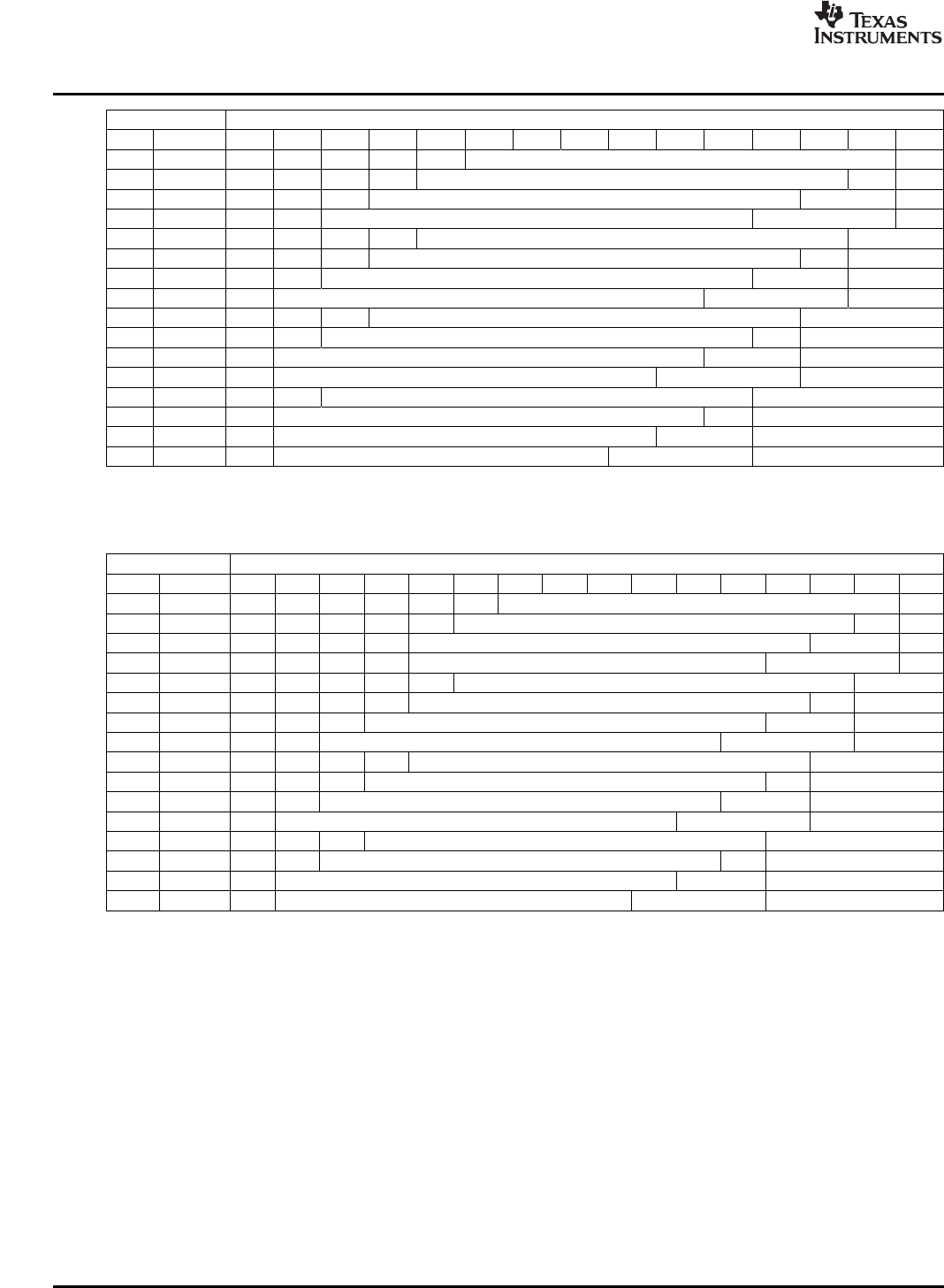

SDCFGBitLogicalAddress

IBANKPAGESIZE31:2827262524232221:1615141312111098:1

00XXXXXXnrb=14

(1)

ncb=8

10XXXXXnrb=14nbb=1ncb=8

20XXXXnrb=14nbb=2ncb=8

30XXXnrb=14nbb=3ncb=8

01XXXXXnrb=14ncb=9

11XXXXnrb=14nbb=1ncb=9

21XXXnrb=14nbb=2ncb=9

31XXnrb=14nbb=3ncb=9

02XXXXnrb=14ncb=10

12XXXnrb=14nbb=1ncb=10

22XXnrb=14nbb=2ncb=10

32Xnrb=14nbb=3ncb=10

03XXXnrb=14ncb=11

13XXnrb=14nbb=1ncb=11

23Xnrb=13nbb=2ncb=11

33Xnrb=12nbb=3ncb=11

(1)

Legend:nrb=numberofrowaddressbits;ncb=numberofcolumnaddressbits;nbb=numberofbankaddressbits;BE=byte

enablebit.

DSPDDR2MemoryController 20SPRUEK5A–October2007

SubmitDocumentationFeedback