www.ti.com

4.1ModuleIDandRevisionRegister(MIDR)

4.2DDR2MemoryControllerStatusRegister(DMCSTAT)

DDR2MemoryControllerRegisters

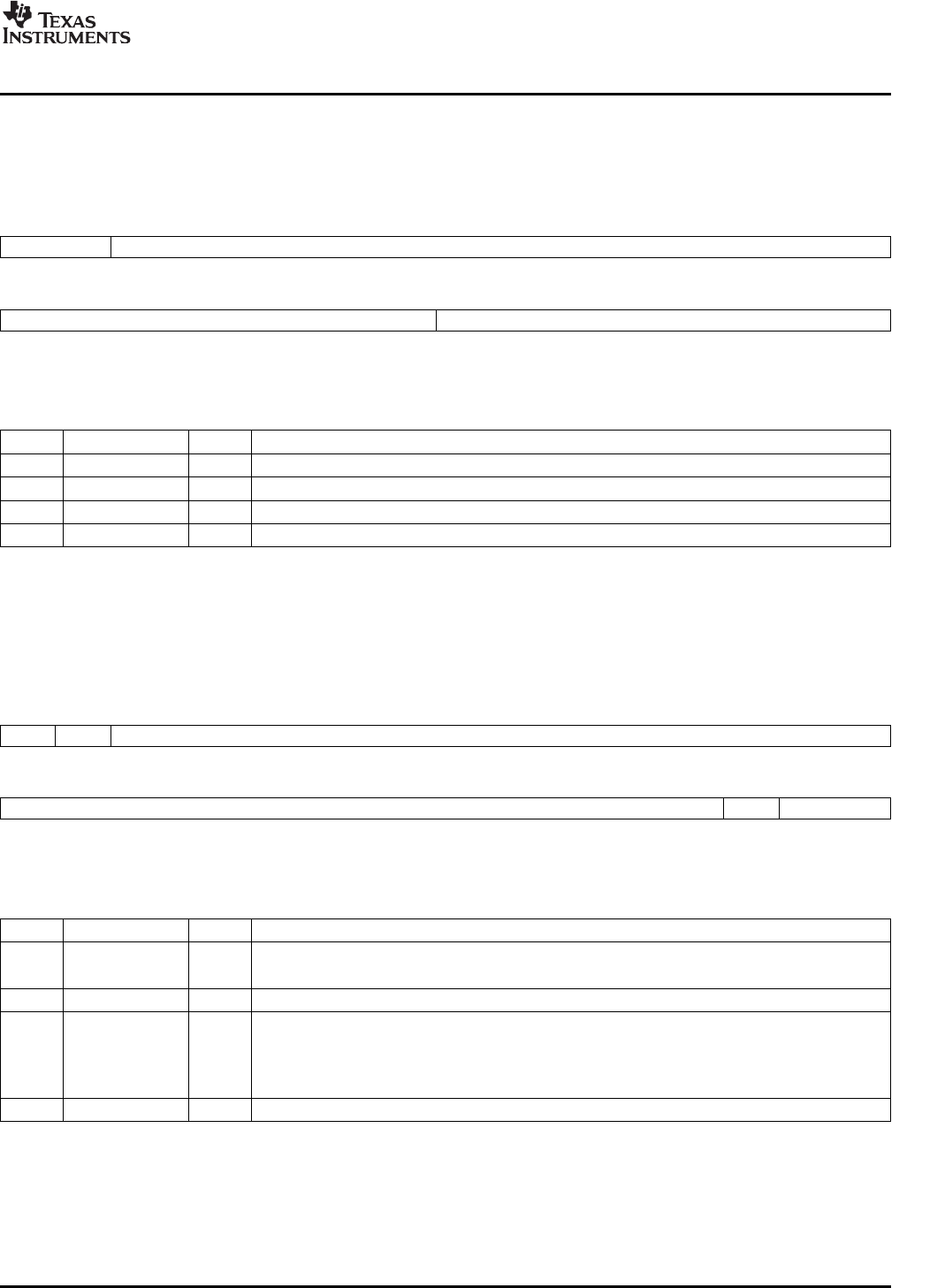

TheModuleIDandRevisionregister(MIDR)isshowninFigure20anddescribedinTable18.

Figure20.ModuleIDandRevisionRegister(MIDR)

31302916

ReservedMOD_ID

R-0x0R-0x0031

15870

MJ_REVMN_REV

R-0x03R-0x0F

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table18.ModuleIDandRevisionRegister(MIDR)FieldDescriptions

BitFieldValueDescription

31-30ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

29-16MOD_IDModuleIDbits.

15-8MJ_REVMajorrevision.

7-0MN_REVMinorrevision.

TheDDR2memorycontrollerstatusregister(DMCSTAT)isshowninFigure21anddescribedin

Table19.

Figure21.DDR2MemoryControllerStatusRegister(DMCSTAT)

31302916

RsvdRsvdReserved

R-0x0R-0x1R-0x0

153210

ReservedIFRDYReserved

R-0x0R-0x0R-0x0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table19.DDR2MemoryControllerStatusRegister(DMCSTAT)FieldDescriptions

BitFieldValueDescription

31Reserved0Reserved.Thevaluealwaysshouldbewrittenas0.writeof1resultsanerrorinfunctionality.

30Reserved1Reserved.Thereservedbitlocationisalwaysreadas1.Avaluewrittentothisfieldhasnoeffect.

29-3Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

2IFRDYDDR2memorycontrollerinterfacelogicreadybit.Theinterfacelogiccontrolsthesignalsusedto

communicatewithDDR2SDRAMdevices.Thisbitdisplaysthestatusoftheinterfacelogic.

0Interfacelogicisnotready;eitherpowereddown,notready,ornotlocked.

1Interfacelogicispoweredup,locked,andreadyforoperation.

1-0Reserved0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

SPRUEK5A–October2007DSPDDR2MemoryController37

SubmitDocumentationFeedback