www.ti.com

2.9Self-RefreshMode

2.10ResetConsiderations

Hard

resetfrom

PLLCTL1

DDR

PSC

DDR2

memory

controller

registers

State

machine

VRST

VCTL_RST

PeripheralArchitecture

Settingtheselfrefresh(SR)bitintheSDRAMrefreshcontrolregister(SDRFC)to1forcestheDDR2

memorycontrollertoplacetheexternalDDR2SDRAMinalow-powermode(selfrefresh),inwhichthe

DDR2SDRAMmaintainsvaliddatawhileconsumingaminimalamountofpower.WhentheSRbitis

asserted,theDDR2memorycontrollercontinuesnormaloperationuntilalloutstandingmemoryaccess

requestshavebeenservicedandtherefreshbackloghasbeencleared.Atthispoint,allopenpagesof

DDR2SDRAMareclosedandaself-refresh(SLFRFR)command(anautorefreshcommandwith

DDR_CKElow)isissued.

TheDDR2memorycontrollerexitstheself-refreshstatewhenamemoryaccessisreceivedorwhenthe

SRbitinSDRFCiscleared.Whileintheself-refreshstate,ifarequestforamemoryaccessisreceived,

theDDR2memorycontrollerservicesthememoryaccessrequest,returningtotheself-refreshstateupon

completion.

TheDDR2memorycontrollerwillnotexittheself-refreshstate(whetherfromamemoryaccessrequestor

fromclearingtheSRbit)untilT_CKE+1cycleshaveexpiredsincetheself-refreshcommandwasissued.

ThevalueofT_CKEisdefinedintheSDRAMtiming2register(SDTIM2).

Afterexitingfromtheself-refreshstate,theDDR2memorycontrollerwillnotimmediatelystartusing

commands.Instead,itwillwaitT_SXNR+1clockcyclesbeforeissuingnon-readcommandsand

T_SXRD+1clockcyclesbeforeissuingreadcommands.TheSDRAMtiming2register(SDTIM2)

programsthevaluesofT_SXNRandT_SXRD.

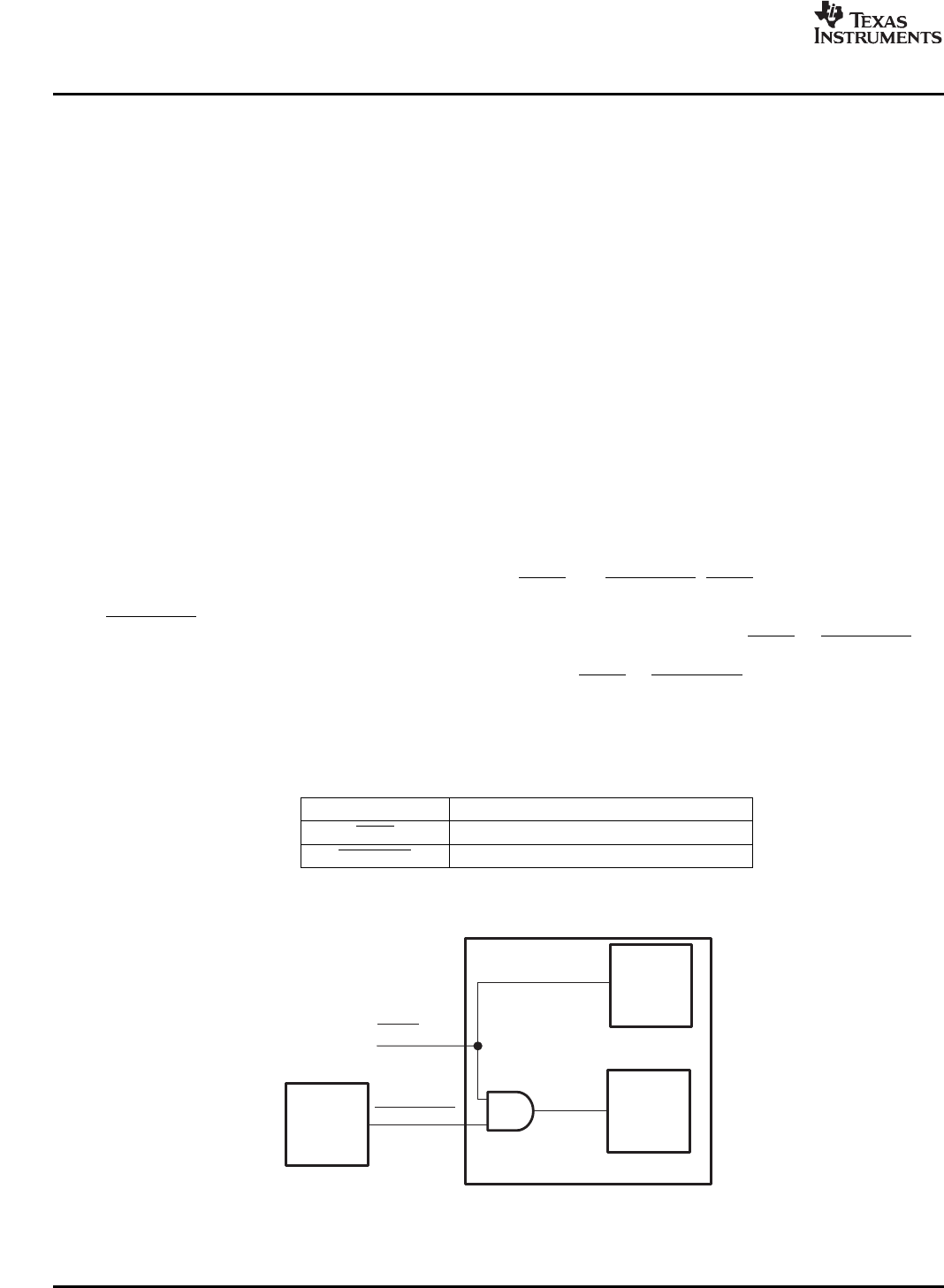

TheDDR2memorycontrollerhastworesetsignals,VRSTandVCTL_RST.VRSTisamodule-levelreset

thatresetsboththestatemachineandtheDDR2memorycontrollermemory-mappedregisters.

VCTL_RSTresetsthestatemachineonly.IftheDDR2memorycontrollerisresetindependentlyofother

peripherals,yoursoftwareshouldnotperformmemoryorregisteraccesseswhileVRSTorVCTL_RSTare

asserted.IfmemoryorregisteraccessesareperformedwhiletheDDR2memorycontrollerisinthereset

state,othermastersmayhang.FollowingtherisingedgeofVRSTorVCTL_RST,theDDR2memory

controllerFIFOsarelost.Table8describesthedifferentmethodsforassertingeachresetsignal.The

PowerandSleepController(PSC)actsasamastercontrollerforpowermanagementforallofthe

peripheralsonthedevice.

Table8.ResetSources

ResetSignalResetSource

VRSTHardware/devicereset

VCTL_RSTPowerandsleepcontroller

Figure16.DDR2MemoryControllerResetBlockDiagram

DSPDDR2MemoryController 26SPRUEK5A–October2007

SubmitDocumentationFeedback